RL78/G10 CHAPTER 6 TIMER ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 222

Dec 22, 2016

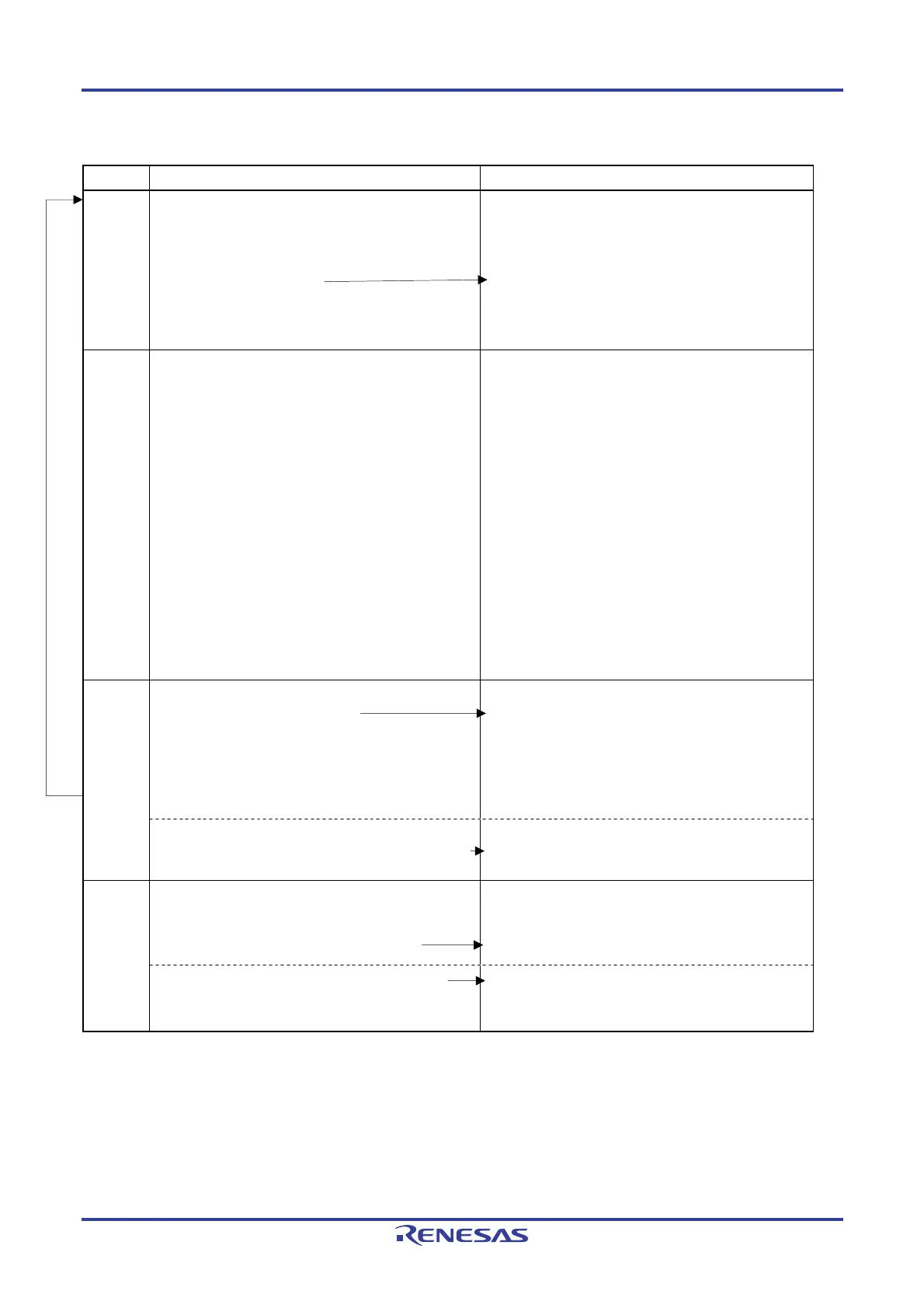

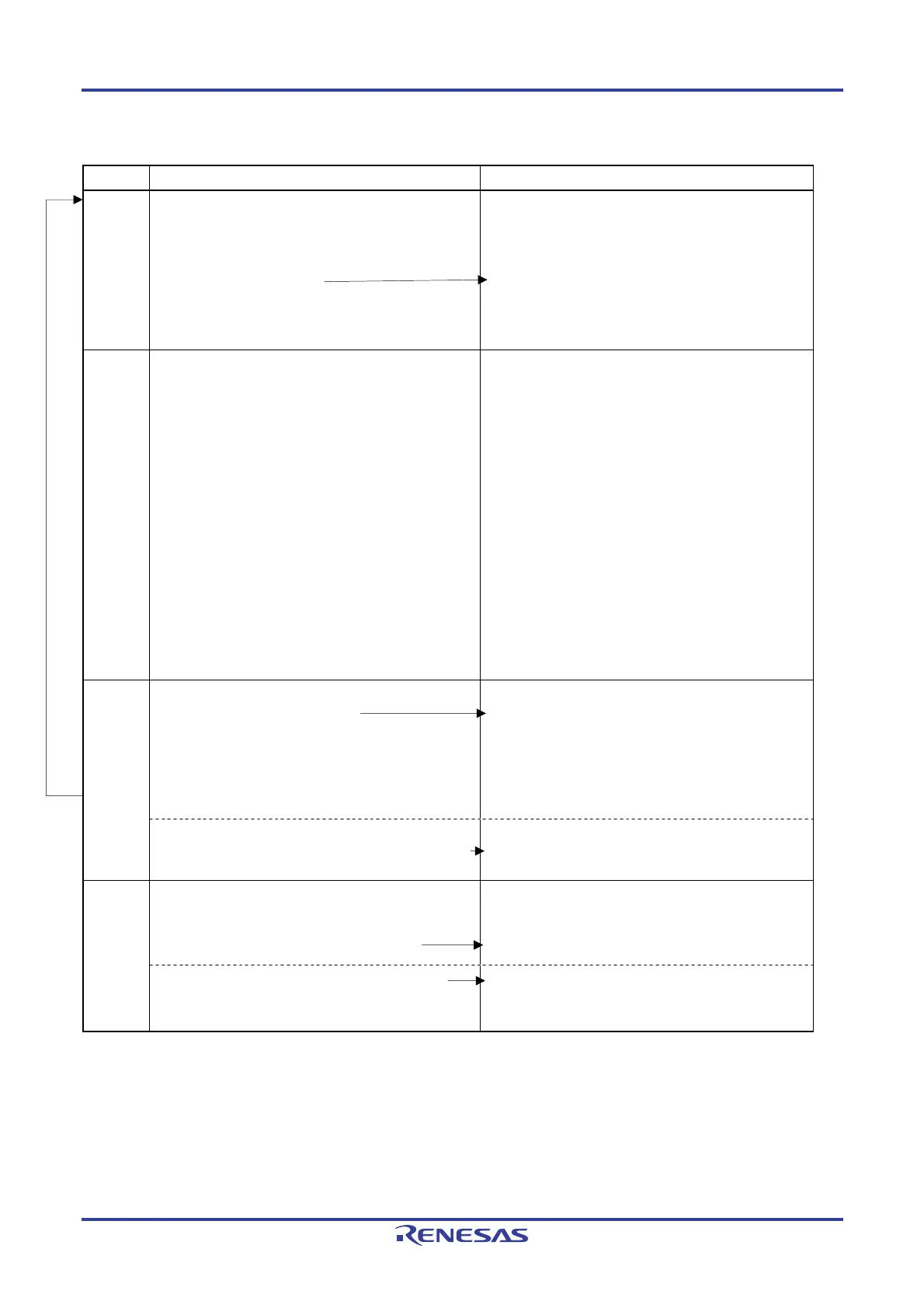

Figure 6-83. Procedure for Using Multiple PWM Output Function (Output Two Types of PWMs) (2/2)

Software Operation Hardware Status

Operation

start

Sets the TOE0p and TOE0q bits of the slave register to 1

and enables the TO0p and TO0q outputs by the count

operation (only when resuming operation).

Sets the target bits of the TS0 register (master and slave)

to 1 at the same time.

The target bits of TS0 register automatically return to 0

because they are trigger bits.

The target bit of the TE0 register is set to 1, and the timer

counter register 00 (TCR00) of the master channel is

loaded with the TDR00 register value and starts counting

down.

During

operation

Changes master channel setting.

The set values of the TDR00 register can be changed

after INTTM00 of the master channel is generated.

The TCR00 register can always be read (for the access

procedure to the TCR00H and TCR00L registers, see

6.2.1 Timer counter register 0n (TCR0n)).

The set values in the target bits of the TMR00, TO0,

TOE0, TOM0, and TOL0 registers cannot be changed.

Changes slave channel setting.

The set values of the TDR0p and TDR0q registers can

be changed after INTTM00 of the master channel is

generated.

The TCR0p and TCR0q register can always be read.

The set values in the target bits of the TO0, TOE0, and

TOL0 registers can be changed.

The set values in the target bits of the TMR0p, TMR0q,

and TOM0 registers cannot be changed.

The timer counter register 00 (TCR00) of the master

channel performs count down operation. When the count

value reaches TCR00 = 0000H, INTTM00 is generated.

At the same time, the value of the TDR00 register is

loaded to the TCR00 register, and the counter starts

counting down again.

At the slave channel, the values of the TDR0p and TDR0q

registers are loaded to the TCR0p and TCR0q registers,

triggered by INTTM00 of the master channel, and the

counter starts counting down. The output levels of TO0p

and TO0q become active one count clock (f

TCLK) after

generation of the INTTM00 output from the master

channel. They become inactive when TCR0p = 0000H

and TCR0q = 0000H, and the counting operation is

stopped at TCR0p = FFFFH and TCR0q = FFFFH.

After that, the above operation is repeated.

Operation

stop

Sets the target bits (master and slave) of the TT0 register

to 1 at the same time.

The target bits of the TT0 register automatically return

to 0 because they are trigger bits.

The target bits of the TE0 register are cleared to 0, and

count operation stops.

The TCR00, TCR0p, and TCR0q registers hold count

value and stop.

The TO0p and TO0q outputs are not initialized but hold

current status.

Clears the TOE0p and TOE0q bits of slave channels to 0

and sets a value to the TO0p and TO0q bits.

The levels set in the TO0p and TO0q bit are output from

the TO0p and TO0q pins.

TAU

stop

To hold the TO0p and TO0q pin output levels

Clears the TO0p and TO0q bits to 0 after

the value to be held (output latch) is set to the port

register.

The TO0p and TO0q pin output levels are held by port

function.

Clears the TAU0EN bit of the PER0 register to 0.

Power-off status

(Clock supply is stopped and SFR of the TAU is

initialized.)

Remark p: Channel number of slave channel 1, q: Channel number of slave channel 2

0 < p < q ≤ 3 (Where p and q are a consecutive integer greater than 0)

Operation is resumed.

Loading...

Loading...