RL78/G10 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 402

Dec 22, 2016

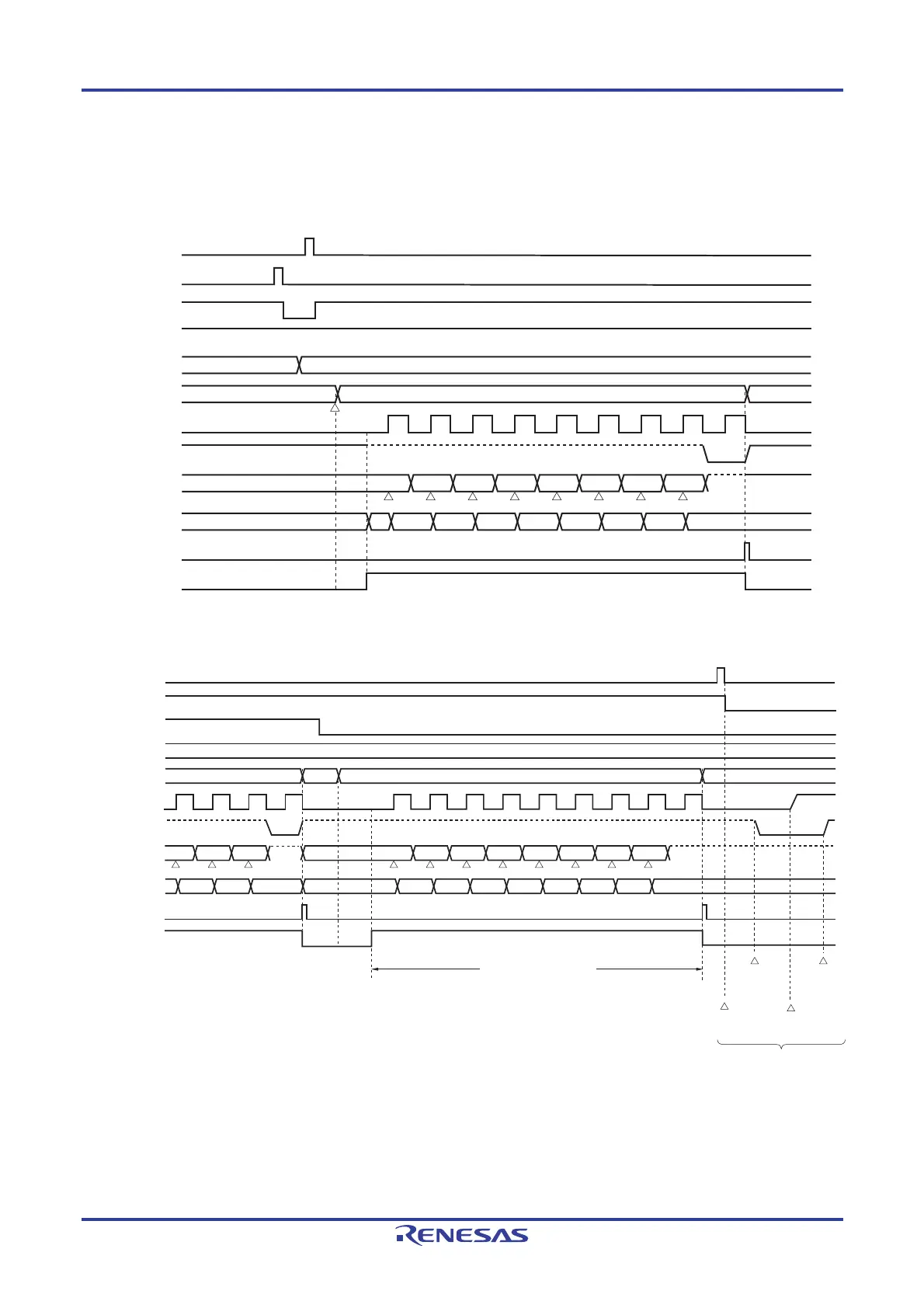

(2) Processing flow

Figure 12-94. Timing Chart of Data Reception

(a) When starting data reception

D7 D6 D5 D4 D3 D2 D1 D0

SS0n

SE0n

SOE0n

SDR0nL

SCLr output

SDAr output

SDAr input

Shift

register 0n

INTIICr

TSF0n

A

CK

ST0n

TXE0n = 0 / RXE0n = 1

TXE0n,

RXE0n

TXE0n = 1 / RXE0n = 0

Shift operation

“H”

Dummy data (FFH)

Receive data

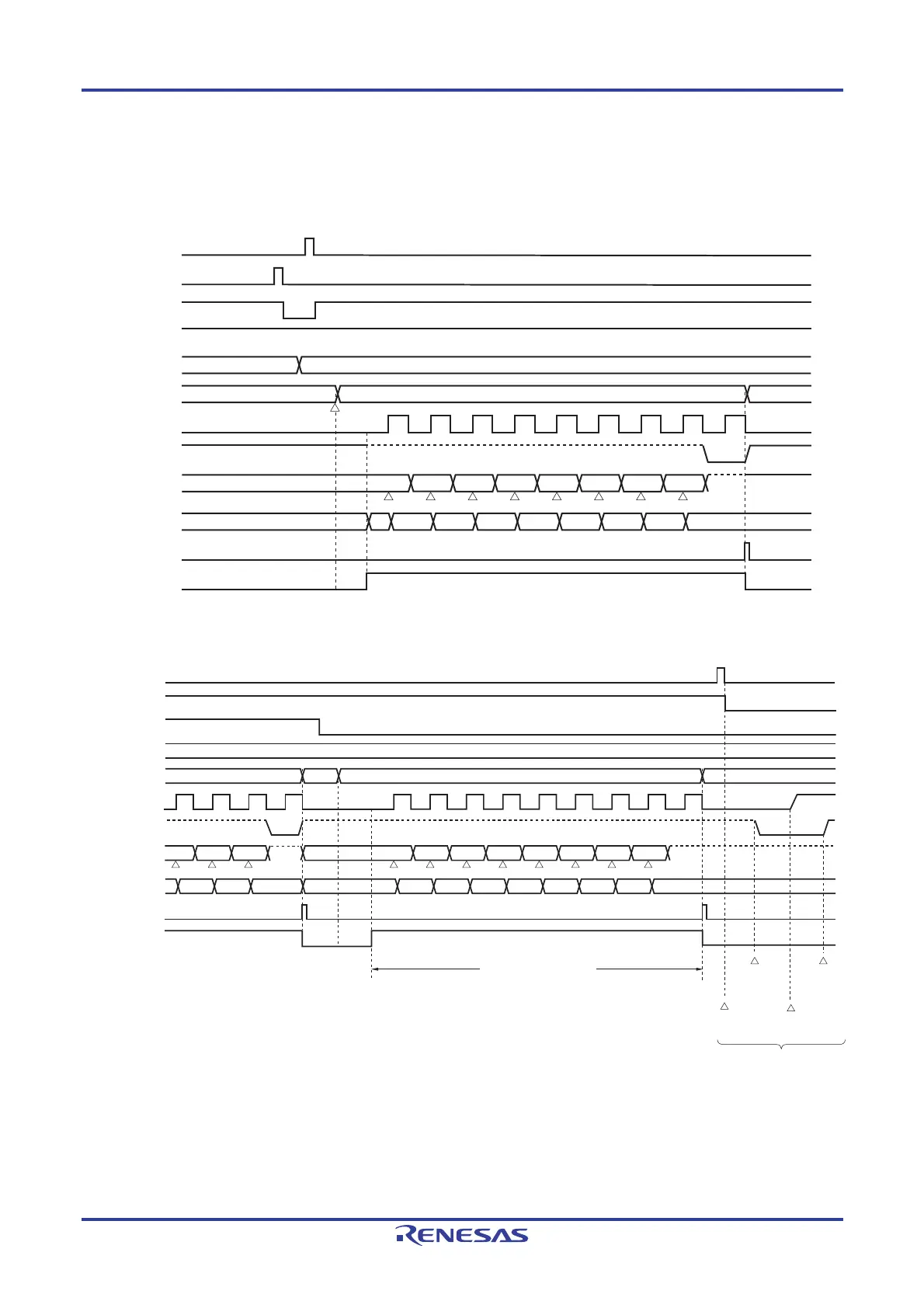

(b) When receiving last data

D7 D6 D5 D4 D3 D2 D1 D0D2 D1 D0

ST0n

SE0n

SOE0n

SDR0nL

SCLr output

SDAr output

SDAr input

Shift

register 0n

INTIICr

TSF0n

Receive data

Receive data

Output is enabled by serial

communication operation

Output is stopped by serial communication operation

NA

CKACK

TXE0n = 0 / RXE0n = 1

TXE0n,

RXE0n

Step condition

Reception of last b

yte

IIC operation stop

SO0n bit

manipulation

CKO0n bit

manipulation

SO0n bit

manipulation

Shift operation

Dummy data (FFH)

Shift operation

Dummy data (FFH)

Remark n = 0 r: IIC number (r = 00)

Loading...

Loading...