RL78/G10 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0384EJ0311 Rev. 3.11 450

Dec 22, 2016

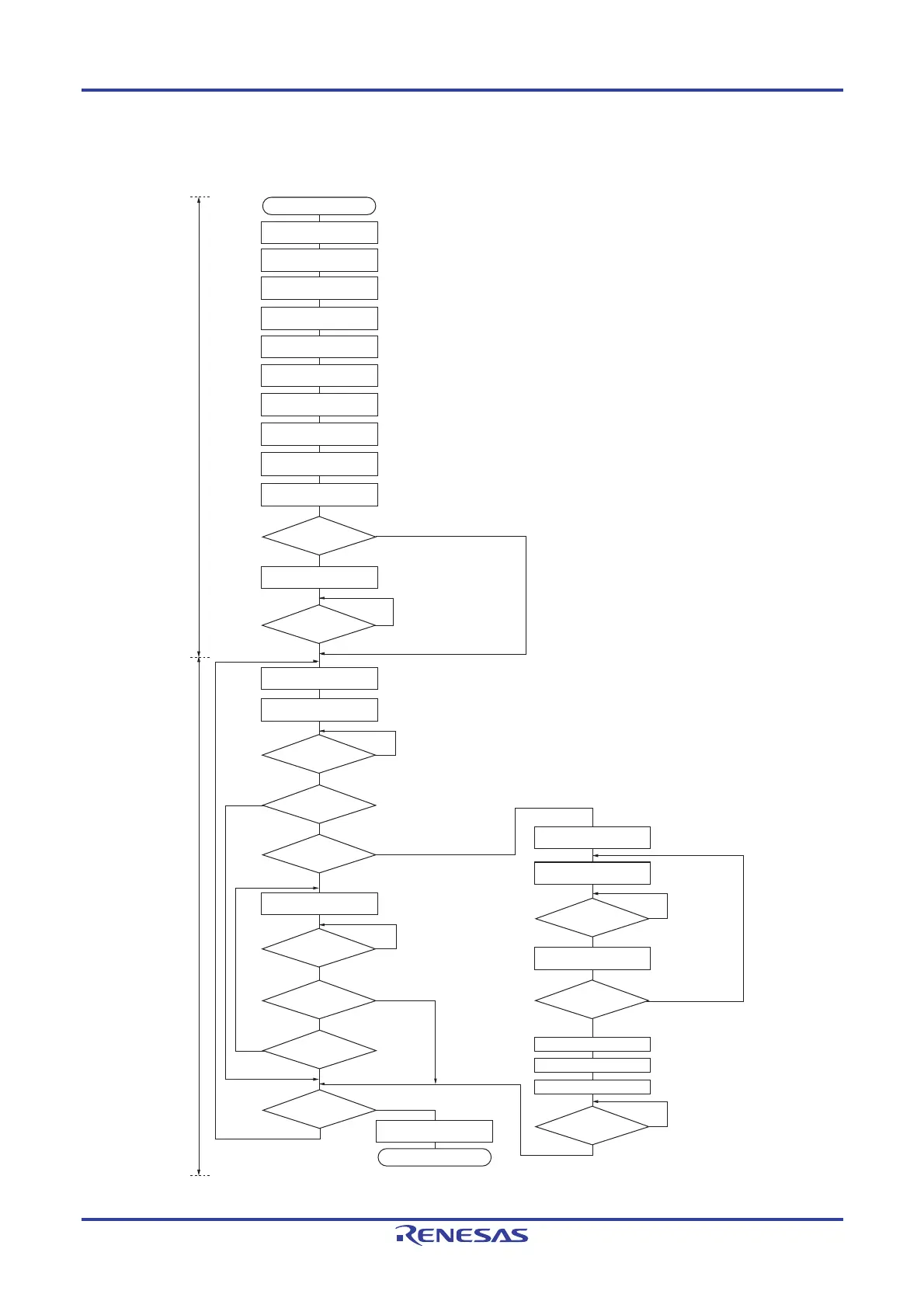

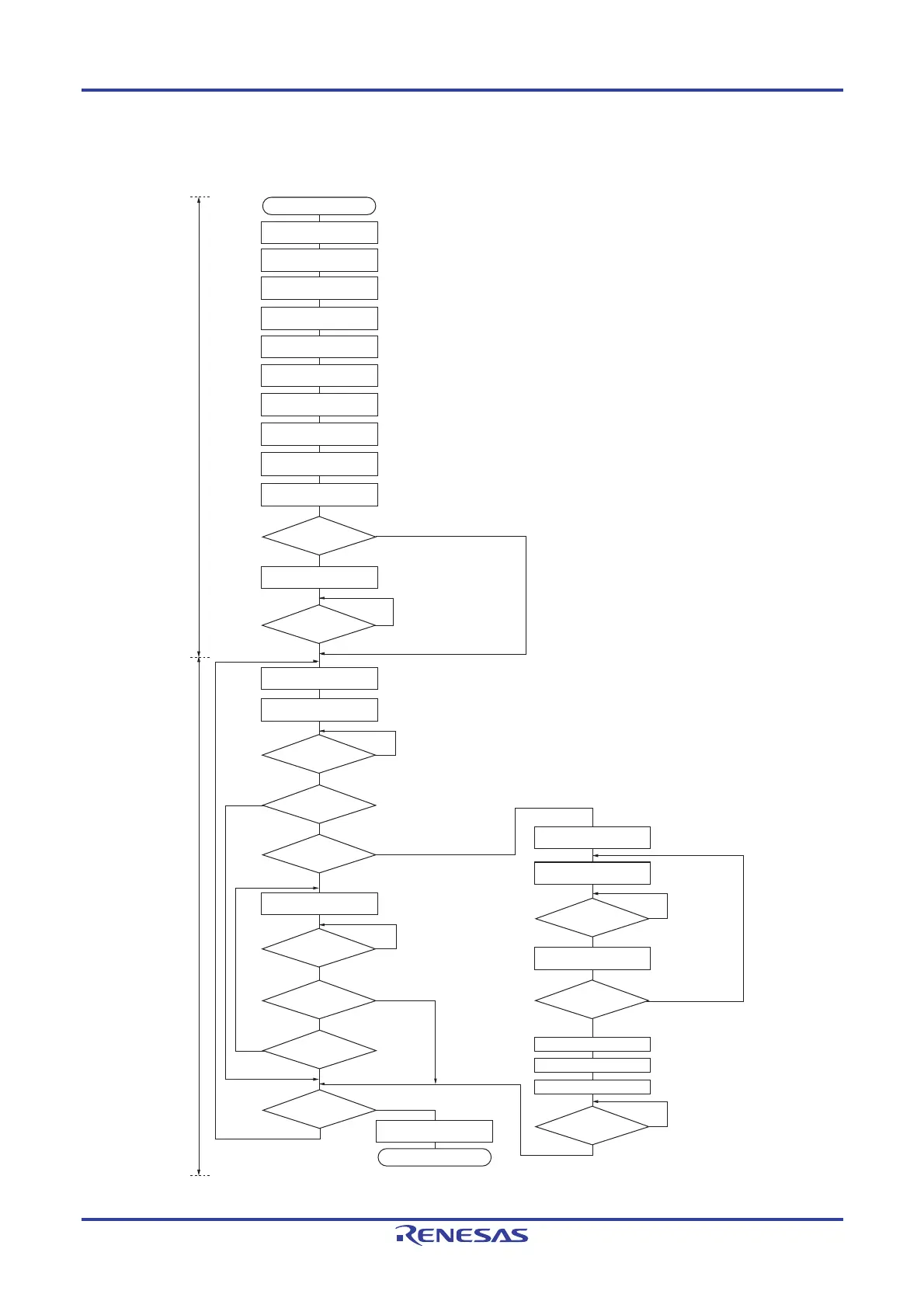

(1) Master operation in single-master system

Figure 13-27. Master Operation in Single-Master System

SPT0 = 1

SPT0 = 1

WREL0 = 1

START

END

ACKE0 = 0

WTIM0 = 1

WREL0 = 1

No

No

Ye s

No

No

No

Ye s

Ye s

Ye s

Ye s

STCEN0 = 1?

ACKE0 = 1

WTIM0 = 0

TRC0 = 1?

ACKD0 = 1?

ACKD0 = 1?

No

Ye s

No

Y

es

Y

es

No

Yes

No

Yes

No

Ye s

No

Ye s

No

STT0 = 1

IICWL0, IICWH0 ← XXH

IICF0 ← 0XH

Setting STCEN0, IICRSV0 = 0

IICCTL00 ← 1XX111XXB

IICE0 = 1

IICCTL00 ← 0XX111XXB

ACKE0 = WTIM0 = SPIE0 = 1

Setting port

Initializing I

Setting PER0 register

2

C bus

Note

SVA0 ← XXH

Writing IICA0

Writing IICA0

Reading IICA0

INTIICA0

interrupt occurs?

End of transfer?

End of transfer?

Restart?

Setting of the port used alternatively as the pin to be used.

First, set the po

(see 13.3.8 Registers controlling port functions of IICA serial input/output pins).

rt to input mode and the output latch to 0

Release the serial interface IICA0 from the reset status and start clock supply.

Setting port

Set the port from input mode to output mode and enable the output of the I

2

C bus

(see 13.3.8 Registers controlling port functions of IICA serial input/output pins).

Sets a transfer clock.

Sets a local address.

Sets a start condition.

Prepares for starting communication

(generates a start condition).

Starts communication

(specifies an address and transfer

direction).

Waits for detection of acknowledge.

Waits for data transmission.

Starts transmission.

Communication processing

Initial setting

Starts reception.

Waits for data

reception.

INTIICA0

interrupt occurs?

Waits for detection

of acknowledge.

Prepares for starting communication

(generates a stop condition).

Waits for detection of the stop condition.

INTIICA0

interrupt occurs?

INTIICA0

interrupt occurs?

INTIICA0

interrupt occurs?

Setting IICCTL01

(Note and Remark are listed on the next page.)

Loading...

Loading...