RL78/G10 CHAPTER 3 CPU ARCHITECTURE

R01UH0384EJ0311 Rev. 3.11 51

Dec 22, 2016

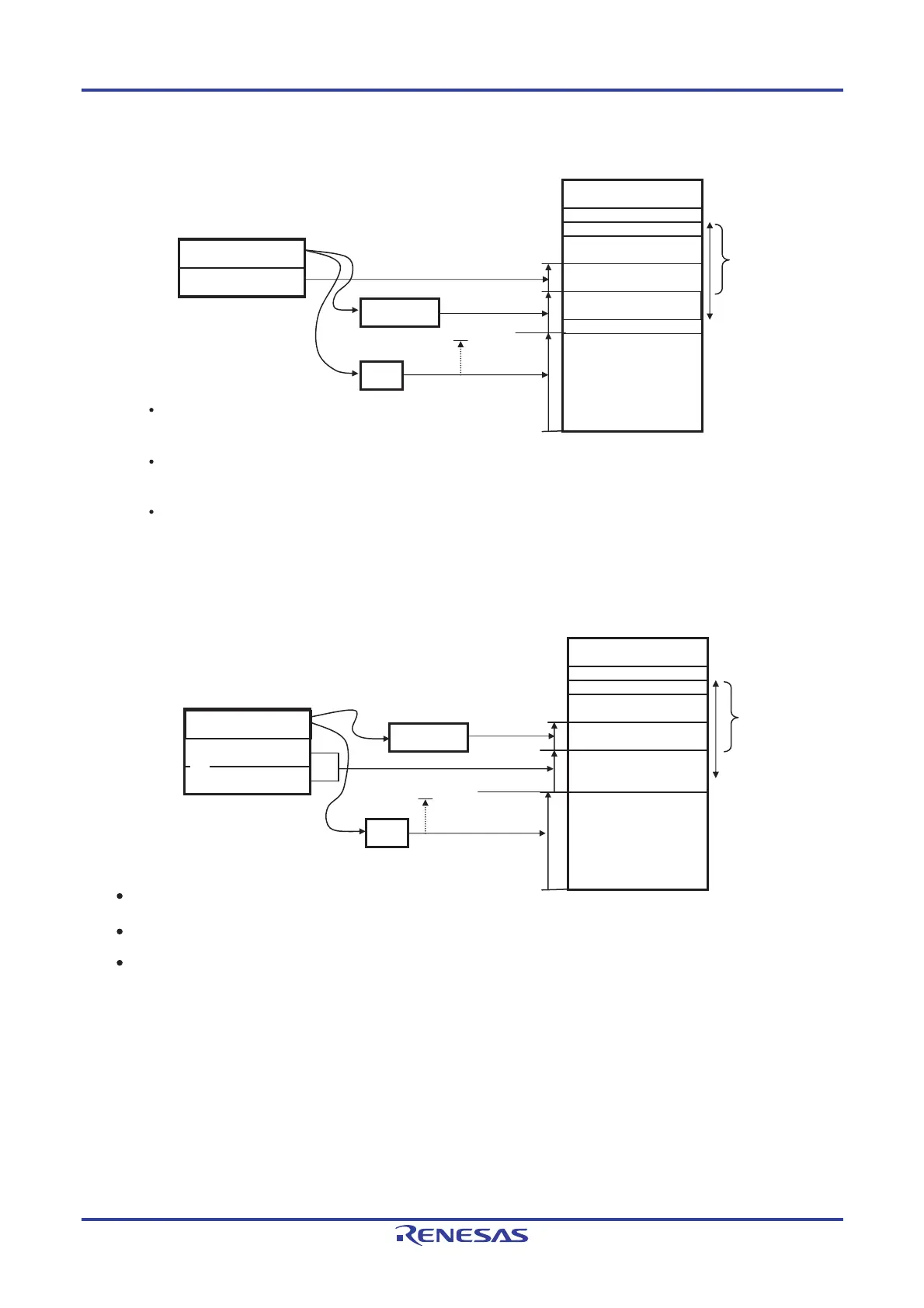

Figure 3-28. Example of ES:[HL + byte], ES:[DE + byte]

XFFFFH

X0000H

rp(HL/DE)

X0000H

ES

ES: [HL + byte], ES: [DE + byte]

Target

array

of data

Address of

an array

OP-code

byte

<3>

Specifies a

64-Kbyte area

Offset

<3>

<1>

Instruction code

<1> <2> <3> <3><1>

<1>

<2>

<2>

<2>

Target memory

Memory

Other data in

the array

The ES register <1> specifies a 64-Kbyte

area within the overall 1-Mbyte space as

the four higher-order bits, X, of the address range.

Either pair of registers <2> specifies the address

where the target array of data starts in the 64-Kbyte

area specified in the ES register <1>.

“byte” <3> specifies an offset within the array to the

target location in memory.

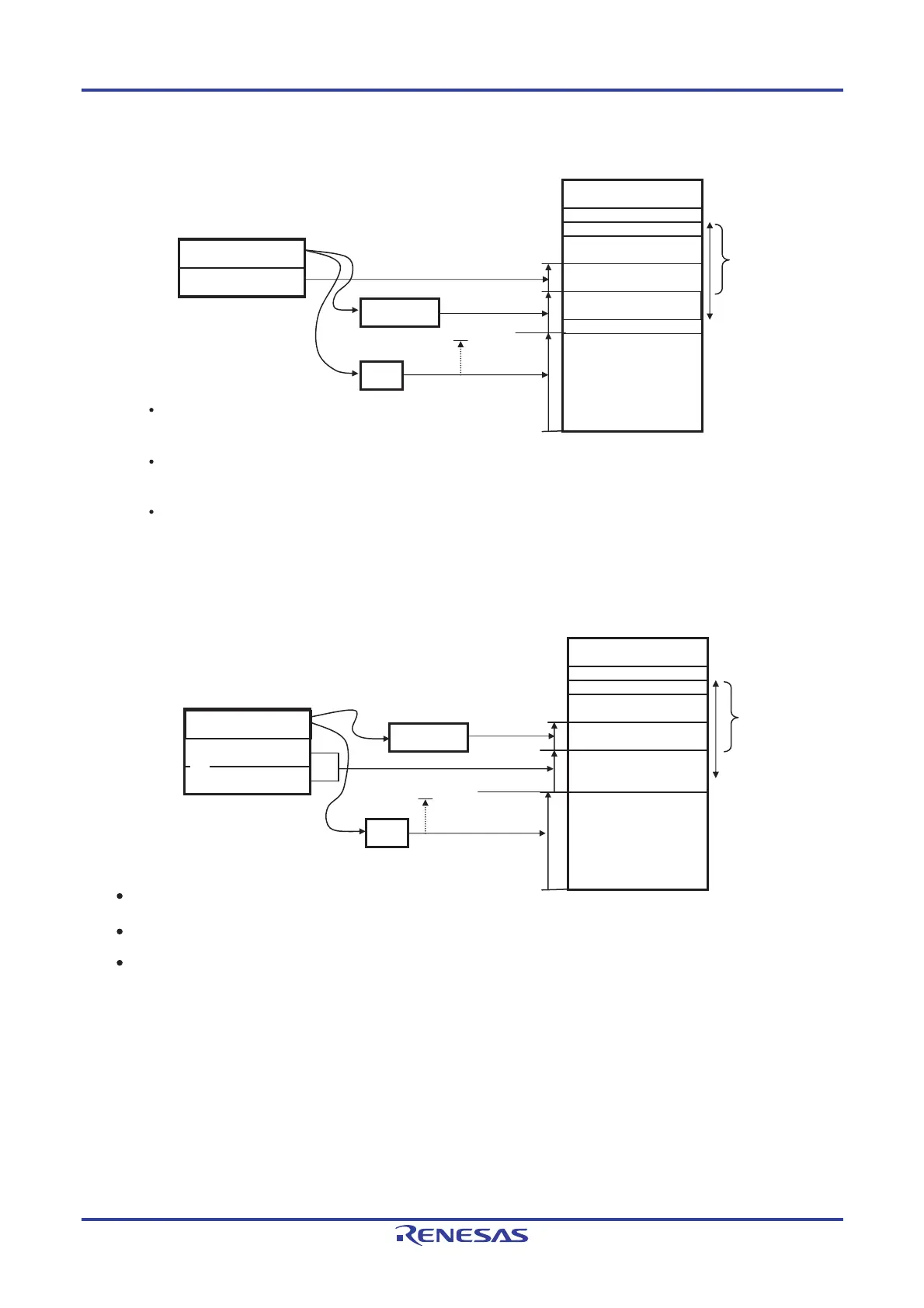

Figure 3-29. Example of ES:word[B], ES:word[C]

XFFFFH

X0000H

r(B/C)

X0000H

ES

ES: word [B], ES: word [C]

Specifies a

64-Kbyte area

Array of

word-sized

data

Offset

Address of a word within an array

Target memory

Instruction code

<1> <2>

<2>

<3> <3>

<3>

<3>

<1>

<1>

<1>

<2>

<2>

Memory

OP-code

Low Addr.

High Addr

.

The ES register <1> specifies a 64-Kbyte area within the overall

1-Mbyte space as the four higher-order bits, X, of the address range.

“word” <2> specifies the address where the target array of word-sized data

starts in the 64-Kbyte area specified in the ES register <1>.

Either register <3> specifies an offset within the array to the target location

in memory.

Loading...

Loading...