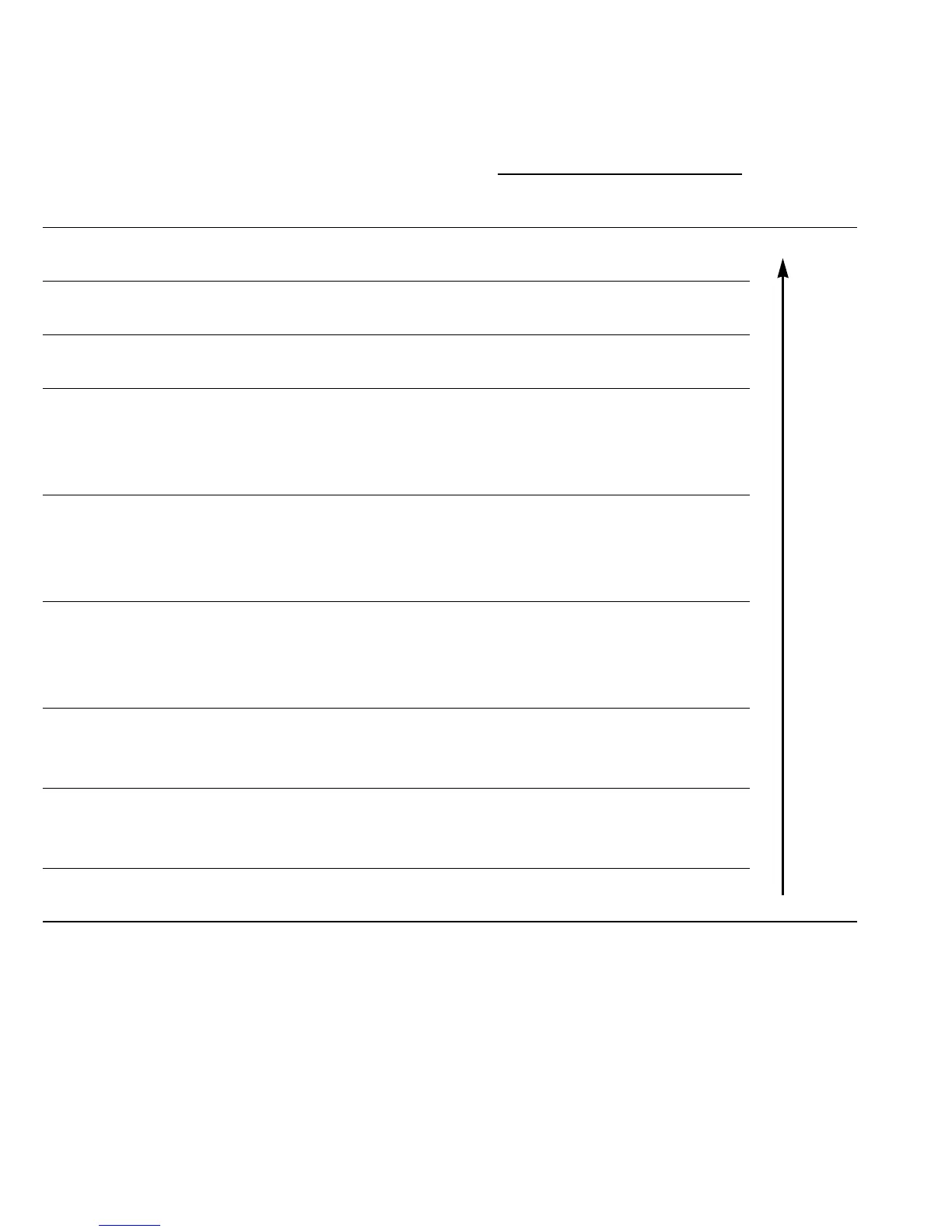

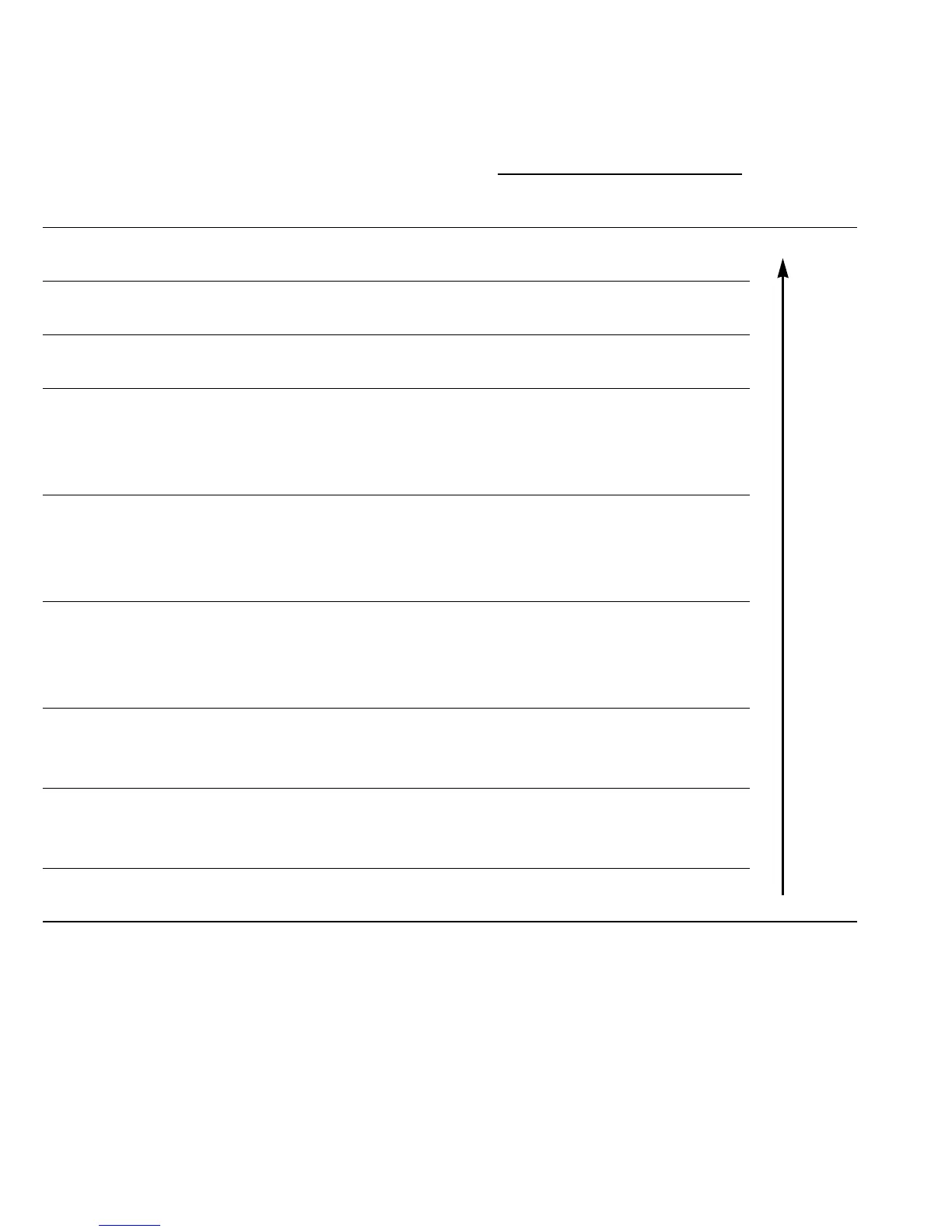

Table 5-2 Interrupts, Vectors, and Priorities

* If two or more interrupts are requested simultaneously, they are handled in order of priority level,

as set in registers IPRA to IPRD. If they have the same priority level because they are requested

from the same on-chip supporting module, they are handled in a fixed priority order within the

module. If they are requested from different modules to which the same priority level is

assigned, they are handled in the order indicated in the right-hand column.

Assignable Priority

Priority Vector Table among

Levels Priority Entry Address Interrupts

(Initial IPR within Minimum Maximum on Same

Interrupt Level) Bits Module Mode Mode Level*

NMI 8 — — H'16 - H'17 H'2C - H'2F High

(8)

IRQ

0 7 to 0 IPRA — H'40 - H'41 H'80 - H'83

(0) bits 6 to 4

IRQ

1 7 to 0 IPRA — H'42 - H'43 H'84 - H'87

(0) bits 2 to 0

16-Bit ICI 7 to 0 IPRB 3 H'48 - H'49 H'90 - H'93

FRT1 OCIA (0) bits 6 to 4 2 H'4A - H'4B H'94 - H'97

OCIB 1 H'4C - H'4D H'98 - H'9B

FOVI 0 H'4E - H'4F H'9C - H'9F

16-Bit ICI 7 to 0 IPRB 3 H'50 - H'51 H'A0 - H'A3

FRT2 OCIA (0) bits 2 to 0 2 H'52 - H'53 H'A4 - H'A7

OCIB 1 H'54 - H'55 H'A8 - H'AB

FOVI 0 H'56 - H'57 H'AC - H'AF

16-Bit ICI 7 to 0 IPRC 3 H'58 - H'59 H'B0 - H'B3

FRT3 OCIA (0) bits 6 to 4 2 H'5A - H'5B H'B4 - H'B7

OCIB 1 H'5C - H'5D H'B8 - H'BB

FOVI 0 H'5E - H'5F H'BC - H'BF

8-Bit CMIA 7 to 0 IPRC 2 H'60 - H'61 H'C0 - H'C3

timer CMIB (0) bits 2 to 0 1 H'62 - H'63 H'C4 - H'C7

OVI 0 H'64 - H'65 H'C8 - H'CB

SCI ERI 7 to 0 IPRD 2 H'68 - H'69 H'D0 - H'D3

RXI (0) bits 6 to 4 1 H'6A - H'6B H'D4 - H'D7

TXI 0 H'6C - H'6D H'D8 - H'DB

A/D ADI 7 to 0 IPRD — H'70 - H'71 H'E0 - H'E3

converter (0) bits 2 to 0 Low

102

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...