10.4 Operation

10.4.1 FRC Incrementation Timing

The FRC increments on a pulse generated once for each period of the selected (internal or

external) clock source.

If external clock input is selected, the FRC increments on the rising edge of the clock signal.

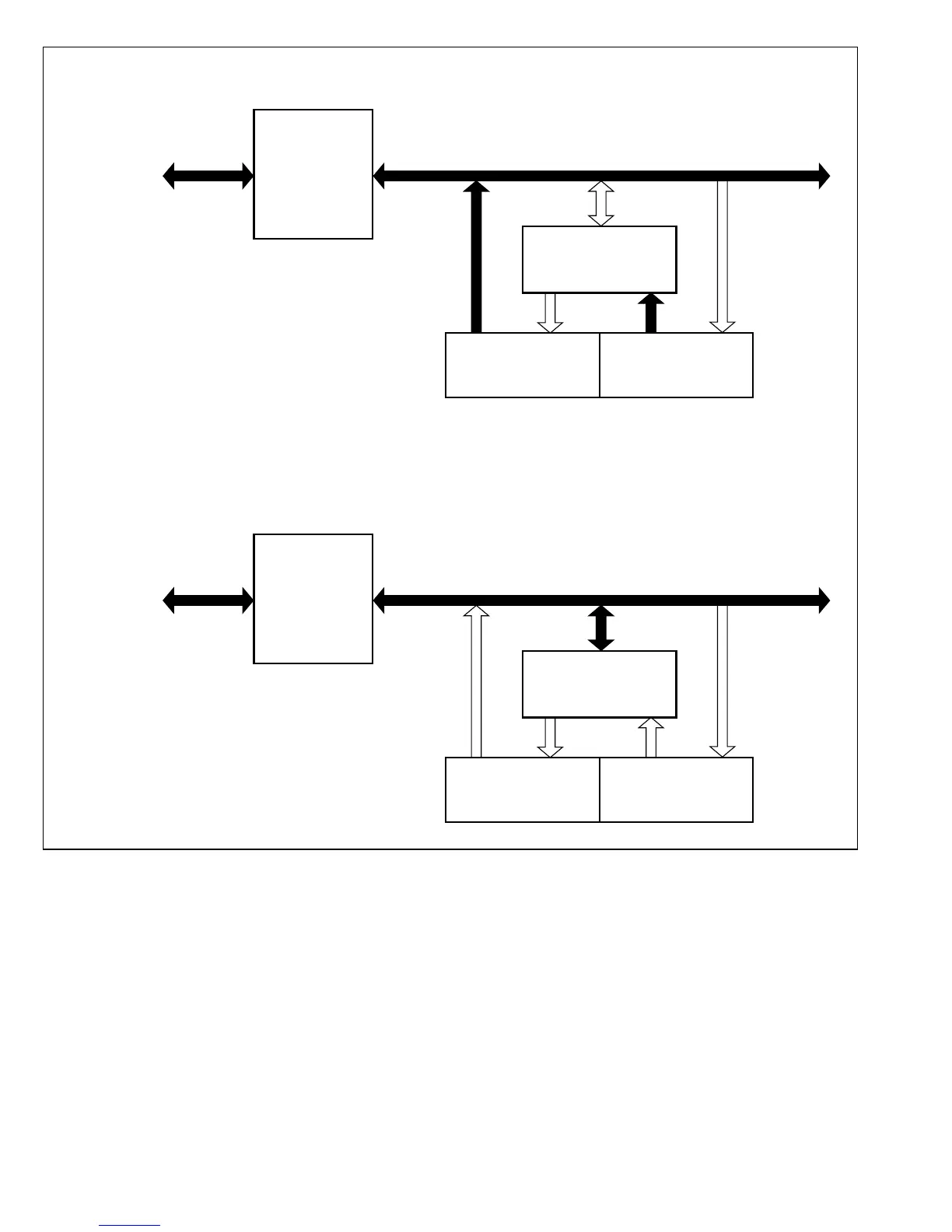

Figure 10-3 shows the increment timing.

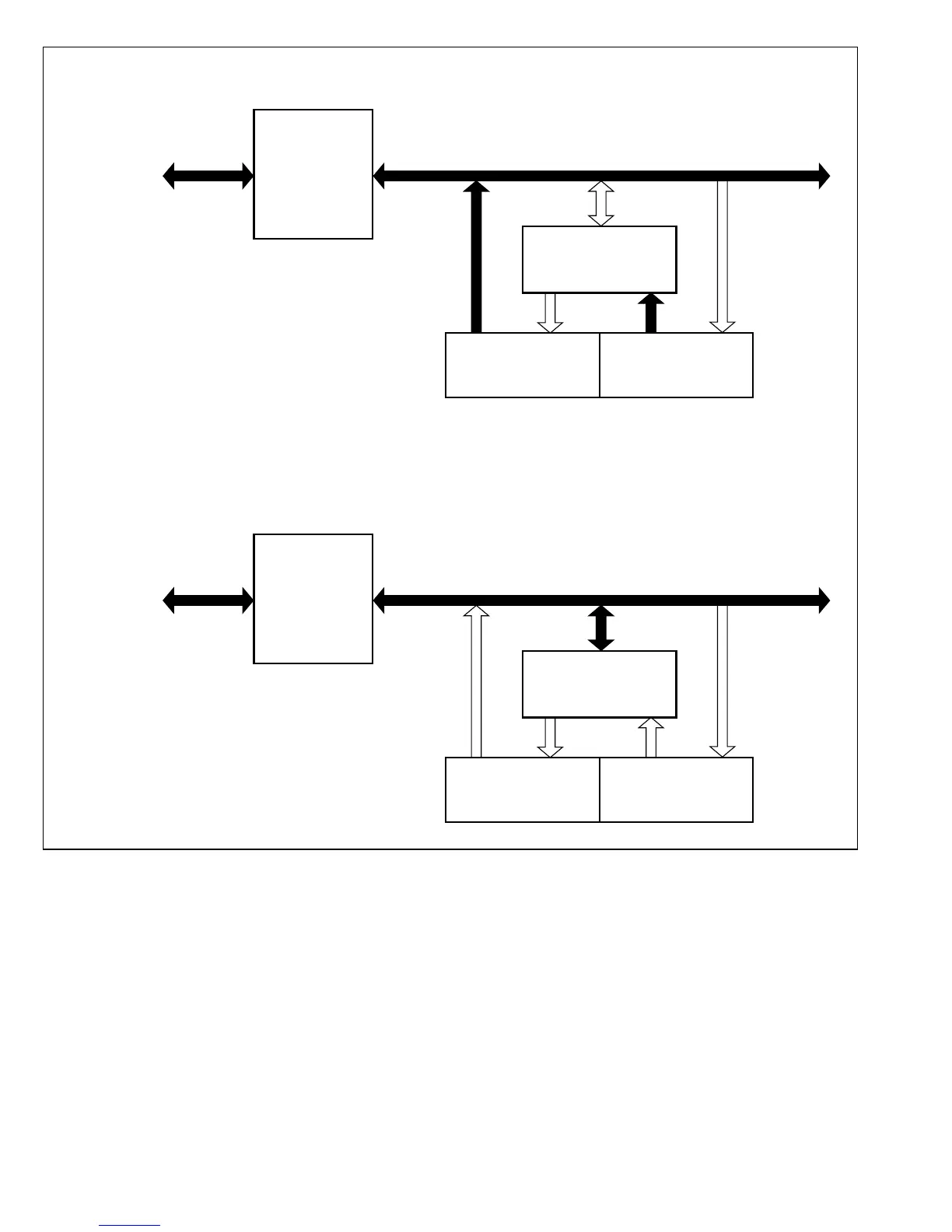

< Lower byte read >

CPU wites

data H’55

Bus interface

TEMP

[H’55]

Module data bus

< Upper byte read >

CPU wites

data H’AA

Bus interface

TEMP

[H’55]

Module data bus

FRCH

[ ]

FRCL

[ ]

FRCH

[H’AA]

FRCL

[H’55]

Figure 10-2 (b) Read Access to FRC (When FRC Contains H'AA55)

190

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...