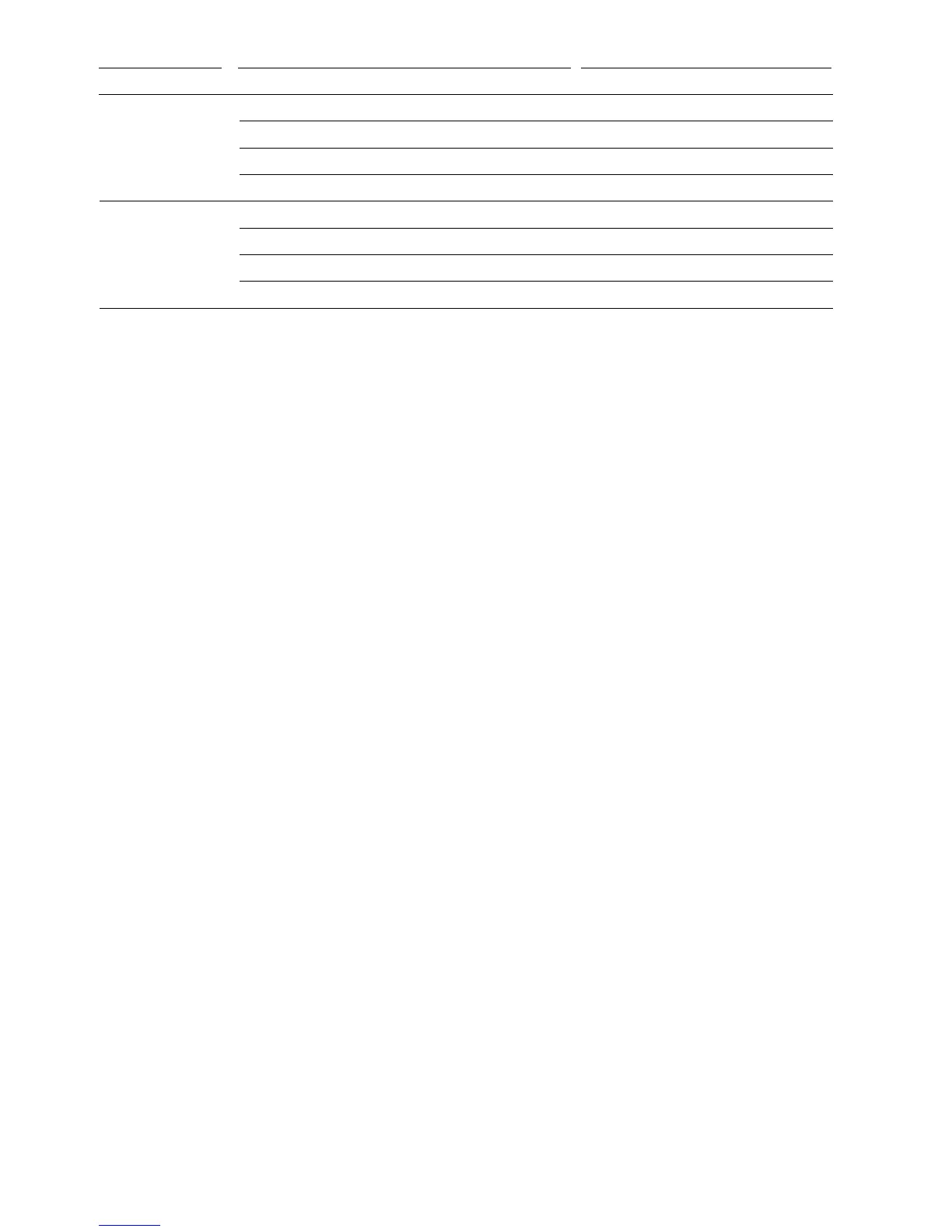

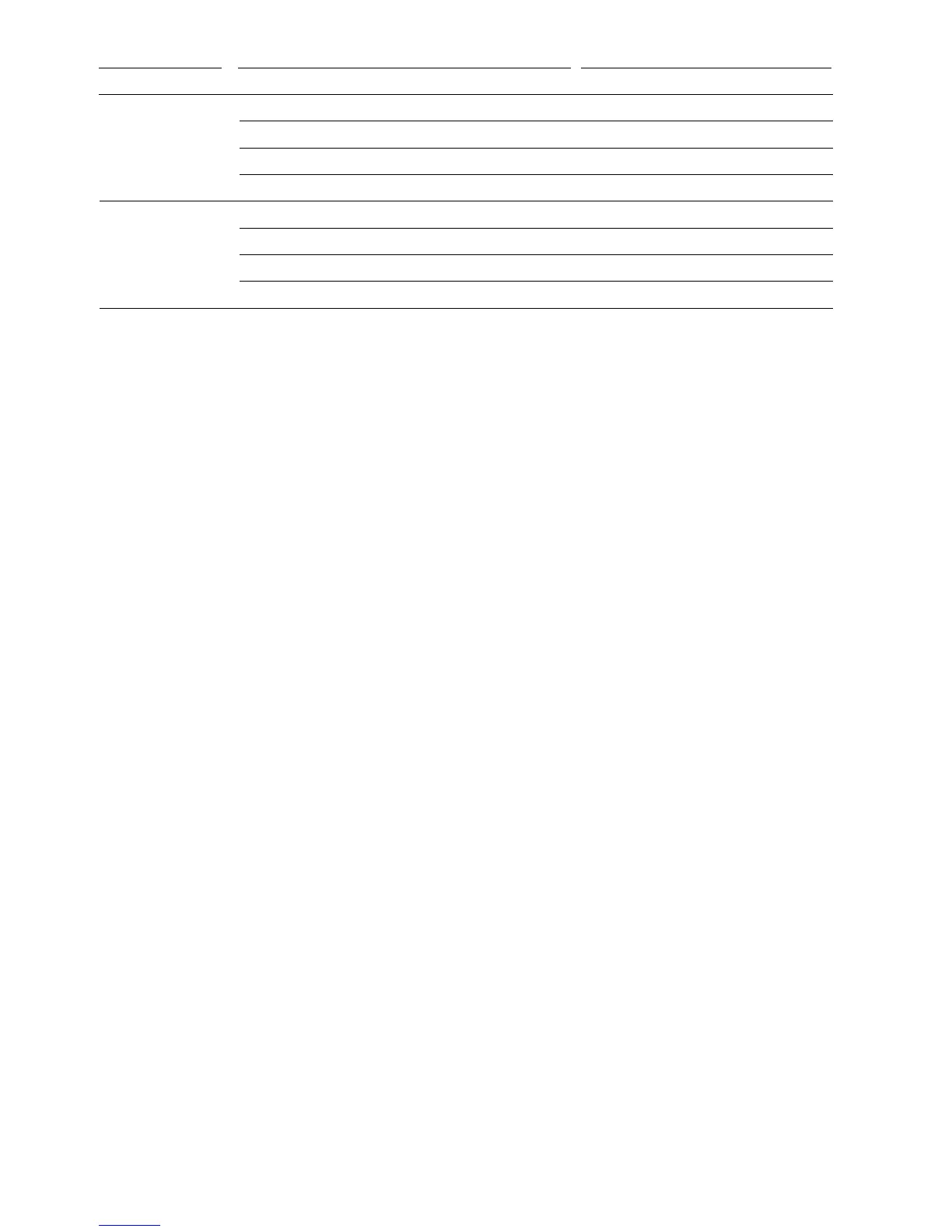

Group Select Channel Select Selected Channels

CH2 CH1 CH0 Single Mode Scan Mode

00 0 AN

0 AN0

01 AN1 AN0 and AN1

10 AN2 AN0 to AN2

11 AN3 AN0 to AN3

10 0 AN4 AN4

01 AN5 AN4 and AN5

10 AN6 AN4 to AN6

11 AN7 AN4 to AN7

15.3 CPU Interface

The A/D data registers (ADDRA to ADDRD) are 16-bit registers. The upper byte of each register

can be read directly, but the lower byte is accessed through an 8-bit temporary register (TEMP).

When the CPU or DTC reads the upper byte of an A/D data register, at the same time as the upper

byte is placed on the internal data bus, the lower byte is transferred to TEMP. When the lower

byte is accessed, the value in TEMP is placed on the internal data bus.

A program that requires all 10 bits of an A/D result should perform word access, or should read

first the upper byte, then the lower byte of the A/D data register. Either way, it is assured of

obtaining consistent data. Consistent data are not assured if the program reads the lower byte first.

A program that requires only 8-bit A/D accuracy should perform byte access to the upper byte of

the A/D data register. The value in TEMP can be left unread.

Figure 15-2 shows the data flow when the CPU (or DTC) reads an A/D data register.

279

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...