5.6 Interrupt Response Time

Table 5-4 indicates the number of states that may elapse between the generation of an interrupt

request and the execution of the first instruction of the interrupt-handling routine, assuming that

the interrupt is not masked and not preempted by a higher-priority interrupt. Since word access is

performed to on-chip memory areas, fastest interrupt service can be obtained by placing the

program in on-chip ROM and the stack in on-chip RAM.

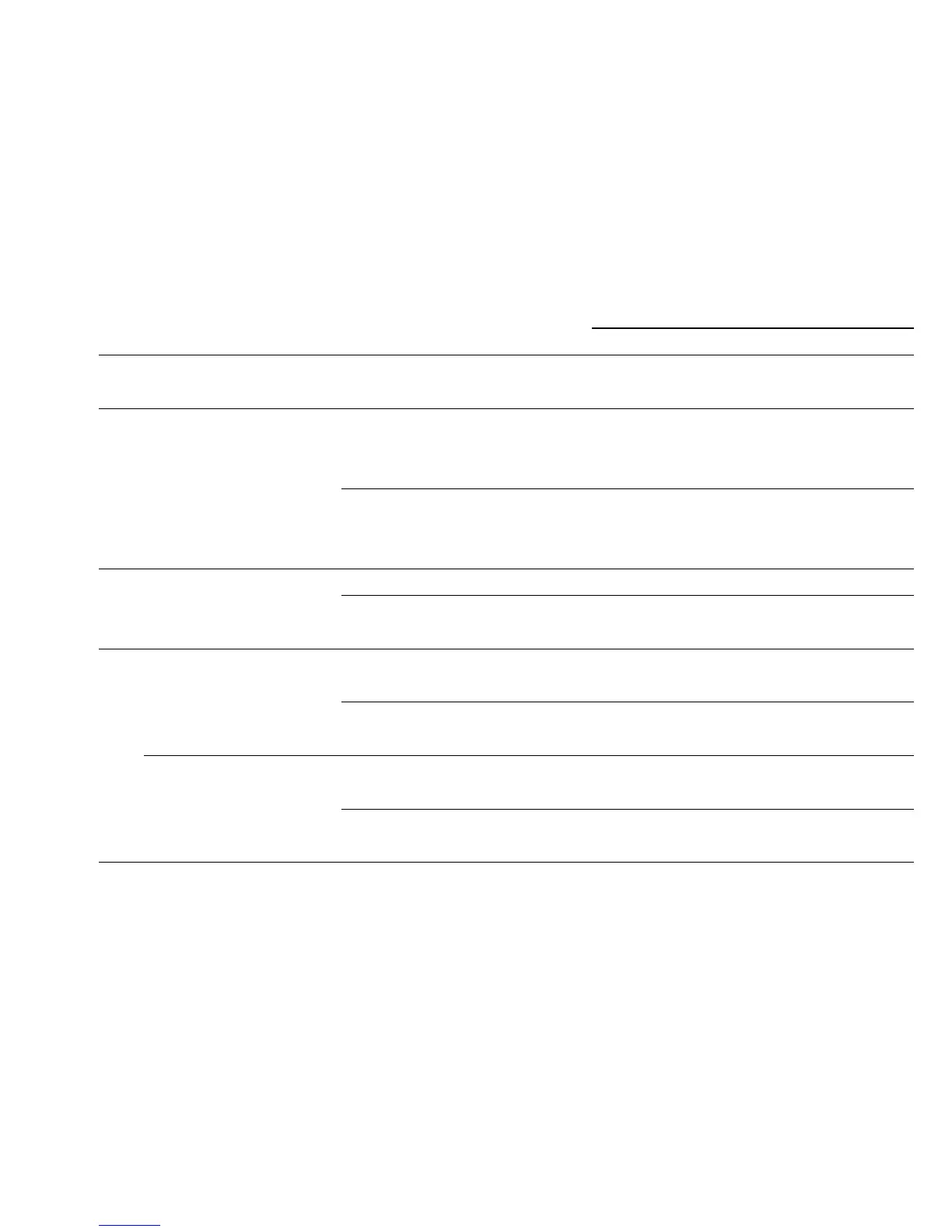

Table 5-4 Number of States before Interrupt Service

Note: m: Number of wait states inserted in external memory access.

Values in parentheses are for the LDM instruction.

Number of States

No. Reason for Wait Minimum Mode Maximum Mode

1 Interrupt priority decision and comparison with 2 states

mask level in CPU status register

2 Maximum number of Instruction is in on-chip x

states to completion memory (x = 38 for LDM instruction specifying

of current instruction all registers)

Instruction is in external y

memory (y = 74 + 16m for LDM instruction

specifying all registers)

3 Saving of PC and SR Stack is in on-chip RAM 16 21

or PC, CP, and SR Stack is in external memory 28 + 6m 41 + 10m

and instruction prefetch

Stack is in Instruction is in on-chip 18 + x 23 + x

on-chip RAM memory (56) (61)

Instruction is in external 18 + y 23 + y

Total memory (92 + 16m) (97 + 16m)

Stack is in Instruction is in on-chip 30 + 6m + x 43 + 10m + x

external RAM memory (68 + 6m) (81 + 10m)

Instruction is in external 30 + 6m + y 43 + 10m + y

memory (104 + 22m) (117 + 26m)

111

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...