3.5.9 Short-Format Instructions

The ADD, CMP, and MOV instructions have special short formats. Table 3-17 lists these short

formats together with the equivalent general formats.

The short formats are a byte shorter than the corresponding general formats, and most of them

execute one state faster.

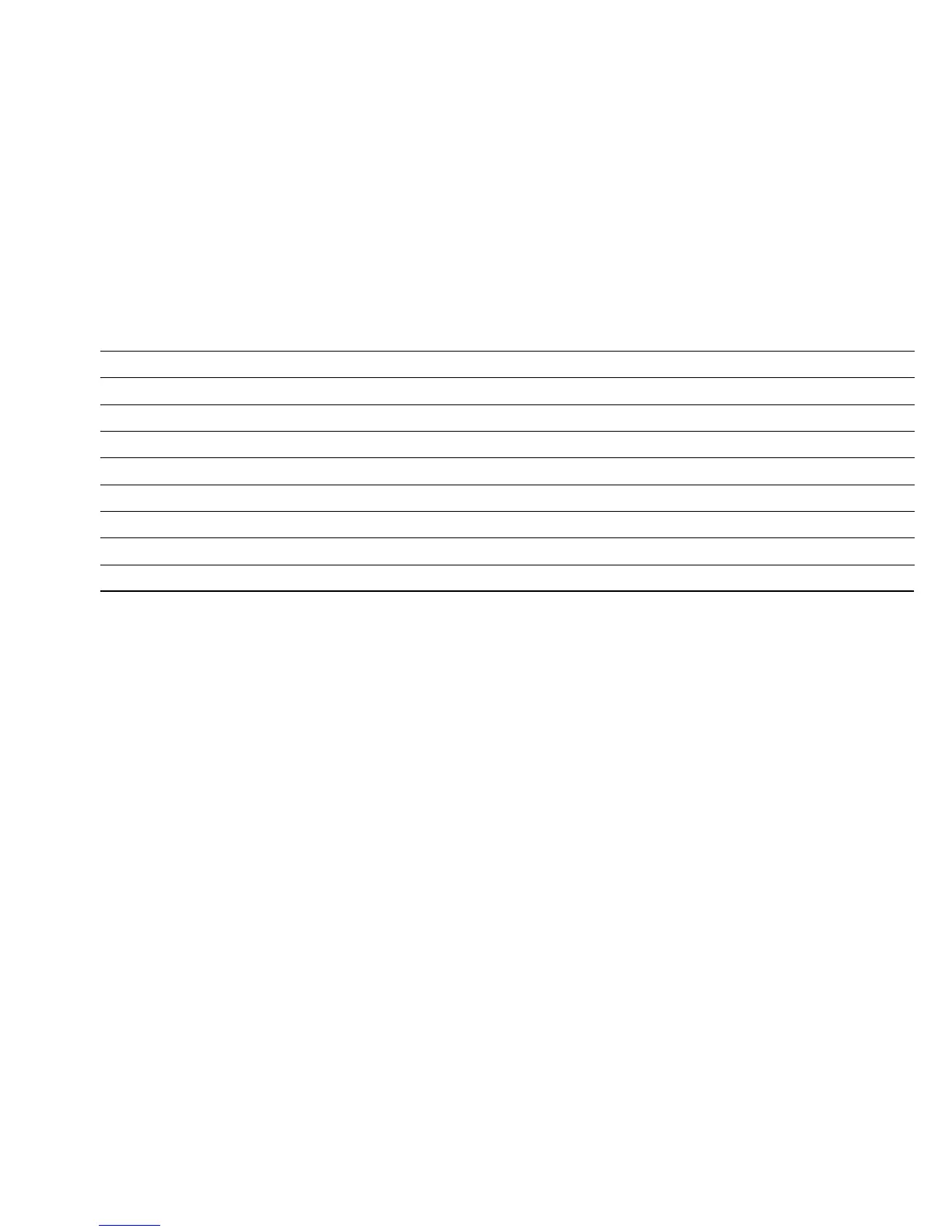

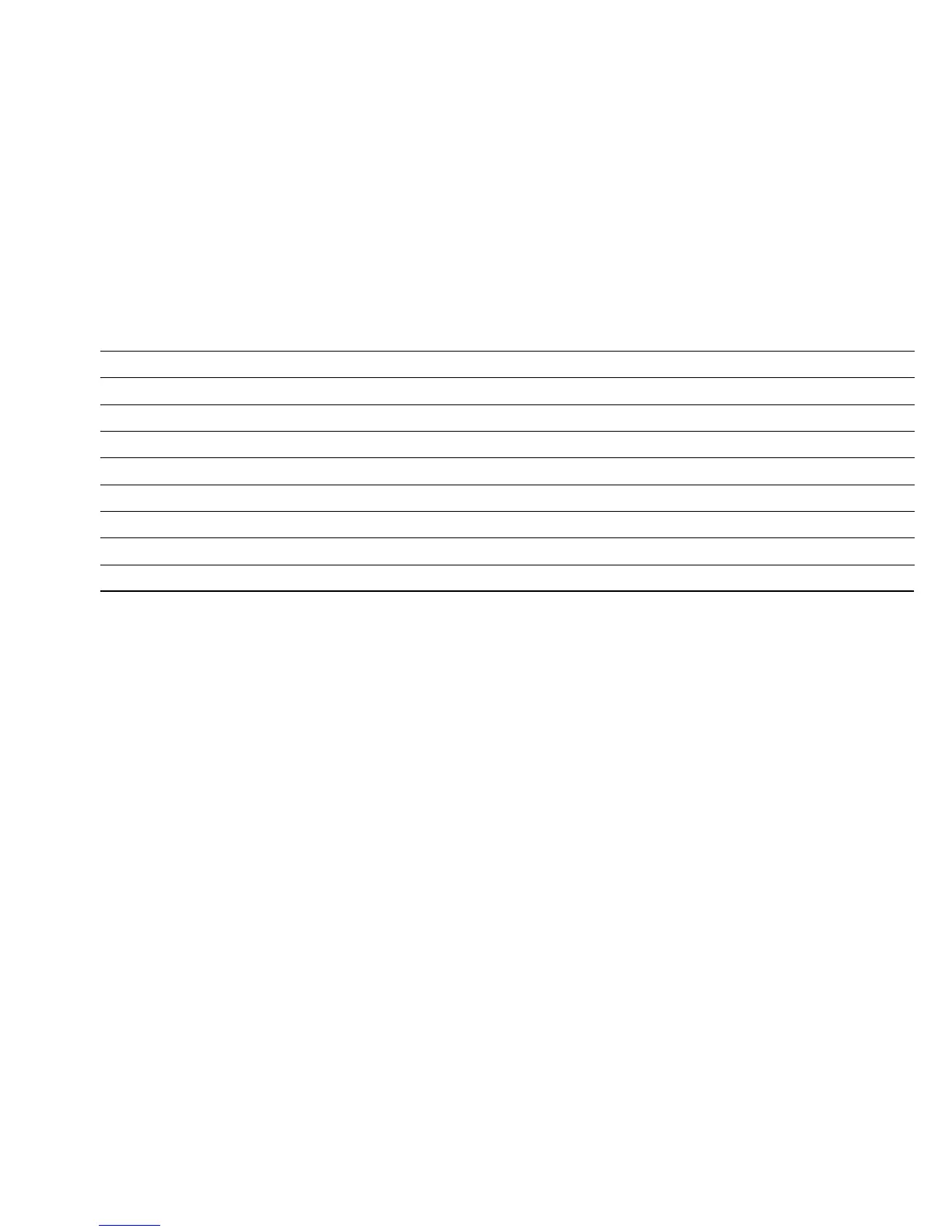

Table 3-17 Short-Format Instructions and Equivalent General Formats

Short-Format Execution Equivalent General- Execution

Instruction Length States

*

2

Format Instruction Length States

*

2

ADD:Q #xx,Rd

*

1

22 ADD:G #xx:8,Rd 33

CMP:E #xx:8,Rd 22 CMP:G.B #xx:8,Rd 33

CMP:I #xx:16,Rd 33 CMP:G.W #xx:16,Rd 44

MOV:E #xx:8,Rd 22 MOV:G.B #xx:8,Rd 33

MOV:I #xx:16,Rd 33 MOV:G.W #xx:16,Rd 44

MOV:L @aa:8,Rd 25 MOV:G @aa:8,Rd 35

MOV:S Rs,@aa:8 25 MOV:G Rs,@aa:8 35

MOV:F @(d:8,R6),Rd 25 MOV:G @(d:8,R6),Rd 35

MOV:F Rs,@(d:8,R6) 25 MOV:G Rs,@(d:8,R6) 35

Notes: * 1 The ADD:Q instruction accepts other destination operands in addition to a general

register, but the immediate data value (#xx) is limited to ±1 or ±2.

* 2 Number of execution states for access to on-chip memory.

3.6 Operating Modes

The CPU operates in one of two modes: the minimum mode or the maximum mode.

These modes are selected by the mode pins (MD2 to MD0 ).

3.6.1 Minimum Mode

The minimum mode supports a maximum address space of 64k bytes. The page registers are

ignored. Instructions that branch across page boundaries (PJMP, PJSR, PRTS, PRTD) are invalid.

62

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...