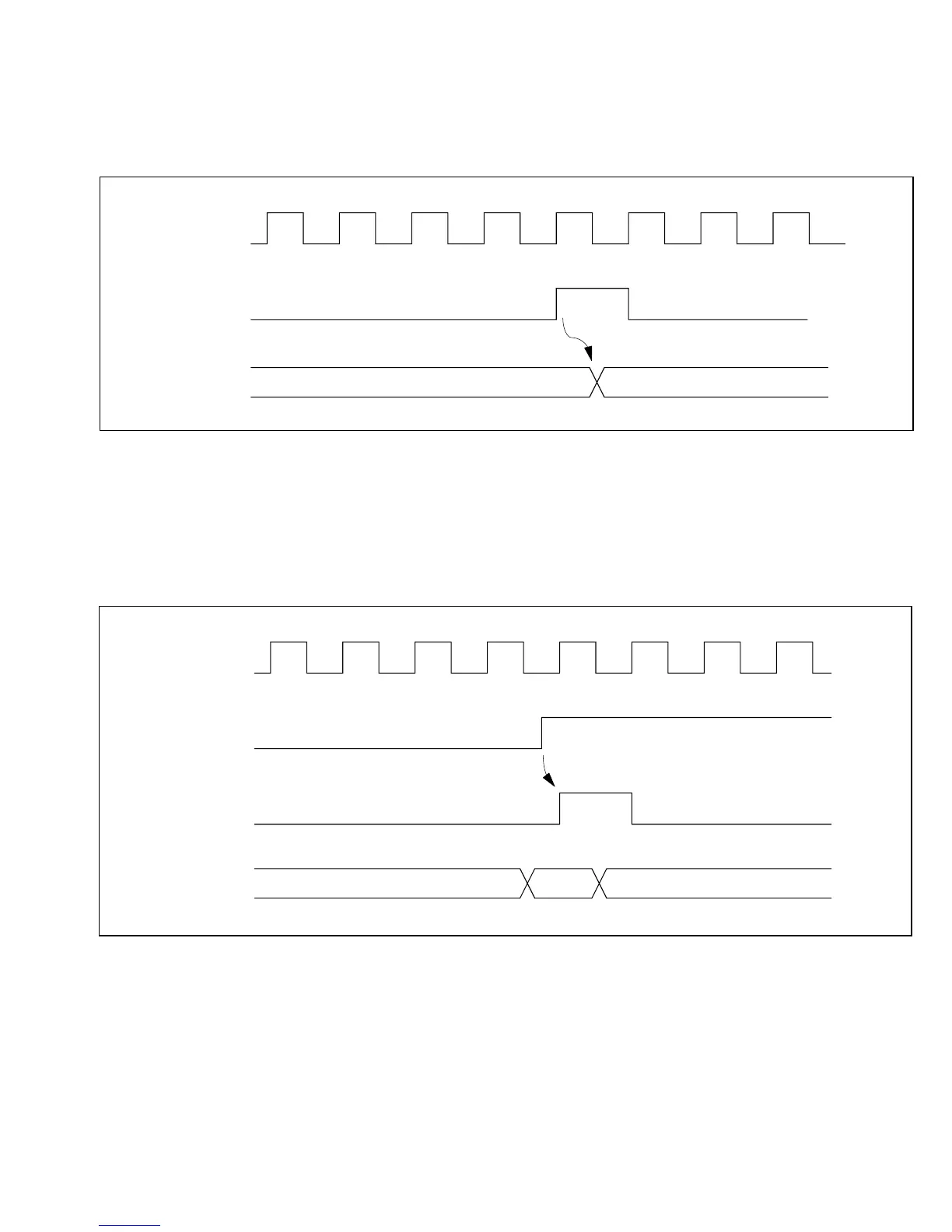

Timing of Compare-Match Clear

Depending on the CCLR1 and CCLR0 bits in the TCR, the timer counter can be cleared when

compare-match A or B occurs. Figure 11-5 shows the timing of this operation.

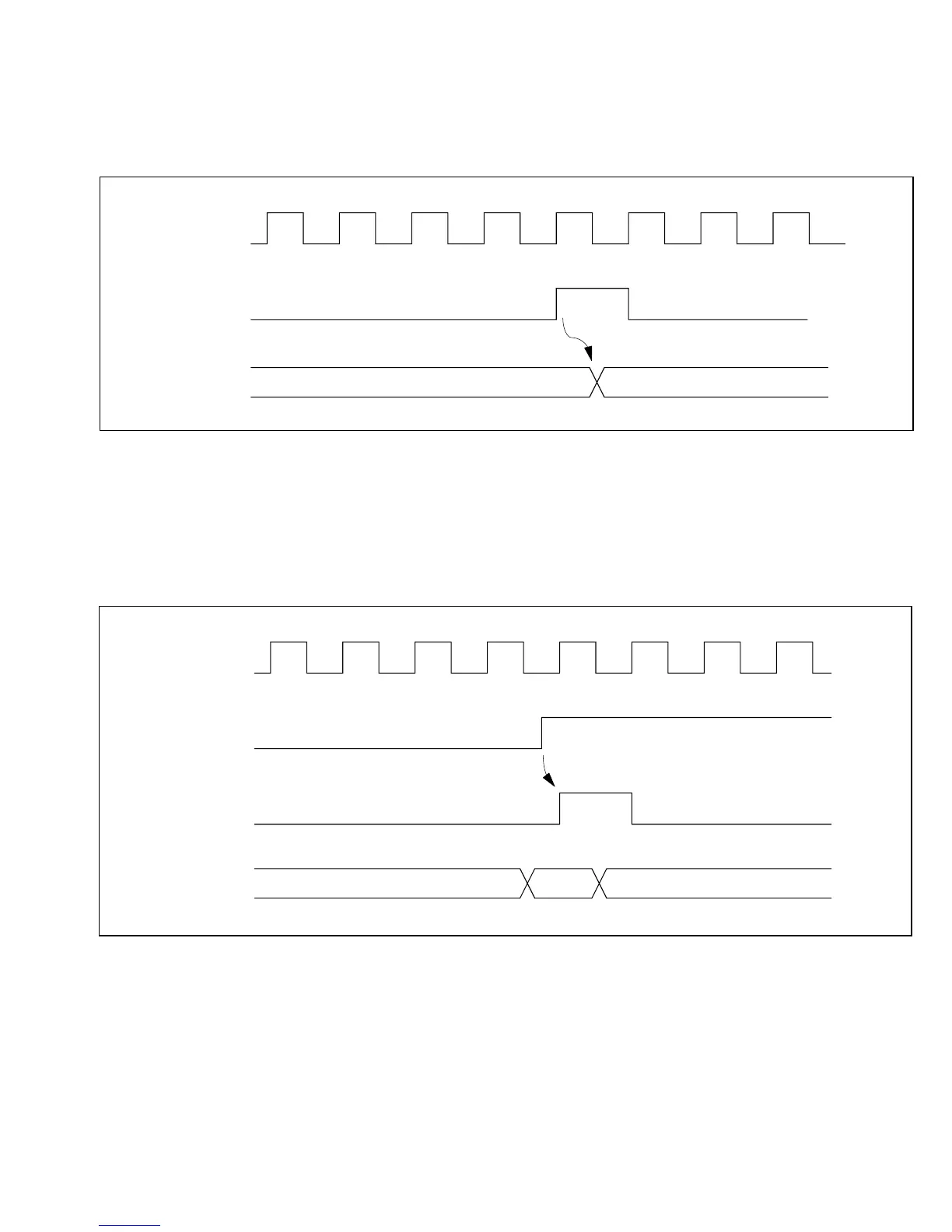

11.3.3 External Reset of TCNT

When the CCLR1 and CCLR0 bits in the TCR are both set to “1,” the timer counter is cleared on

the rising edge of an external reset input. Figure 11-6 shows the timing of this operation.

N H’00

Internal

compare-match

signal

TCNT

ø

H’00N – 1 NTCNT

Internal clear

pulse

External reset

input (TMRI)

ø

Figure 11-5 Timing of Compare-Match Clear

Figure 11-6 Timing of External Reset

217

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...