4-6 Product Principle

4.2.4 ECG Module

Input

protection

LA_IN

RA_IN

LL_IN

MINDRAY ASIC

LA

RA

LL

SPI

RESET

Reset

(TPS3828)

JTAG

Upper

machine

UART

iso

lat

ion

DC_IN

UART

12V

POWER

ADC

tra

nsf

orm

er

+

-

+

-

+

-

+

-

+

-

+

-

ADC

Input Buffer Amplifier

High-pass

filter wave

Low-pass

filter

wave

MCU

(STM32F205

)

Clock

(12MHz)

Offset

adjustment

High-pass

filter wave

Amplitude

adjustment

Clock

(11.0592MHz)

High-pass

filter wave

Breathi

ng test

wave

Low-pass filter

wave

Carrier

circuit

Buffering

circuit

ECG

DC_IN

RESPIRATION

PWM

Simulati

on

switch

(CD4053)

Via simulation switch

RA-LA or RA-LL

PCG

High-pass

filter wave

Amplitude

adjustment

Offset

adjustment

ADC

PCG

Low-pass

filter

wave

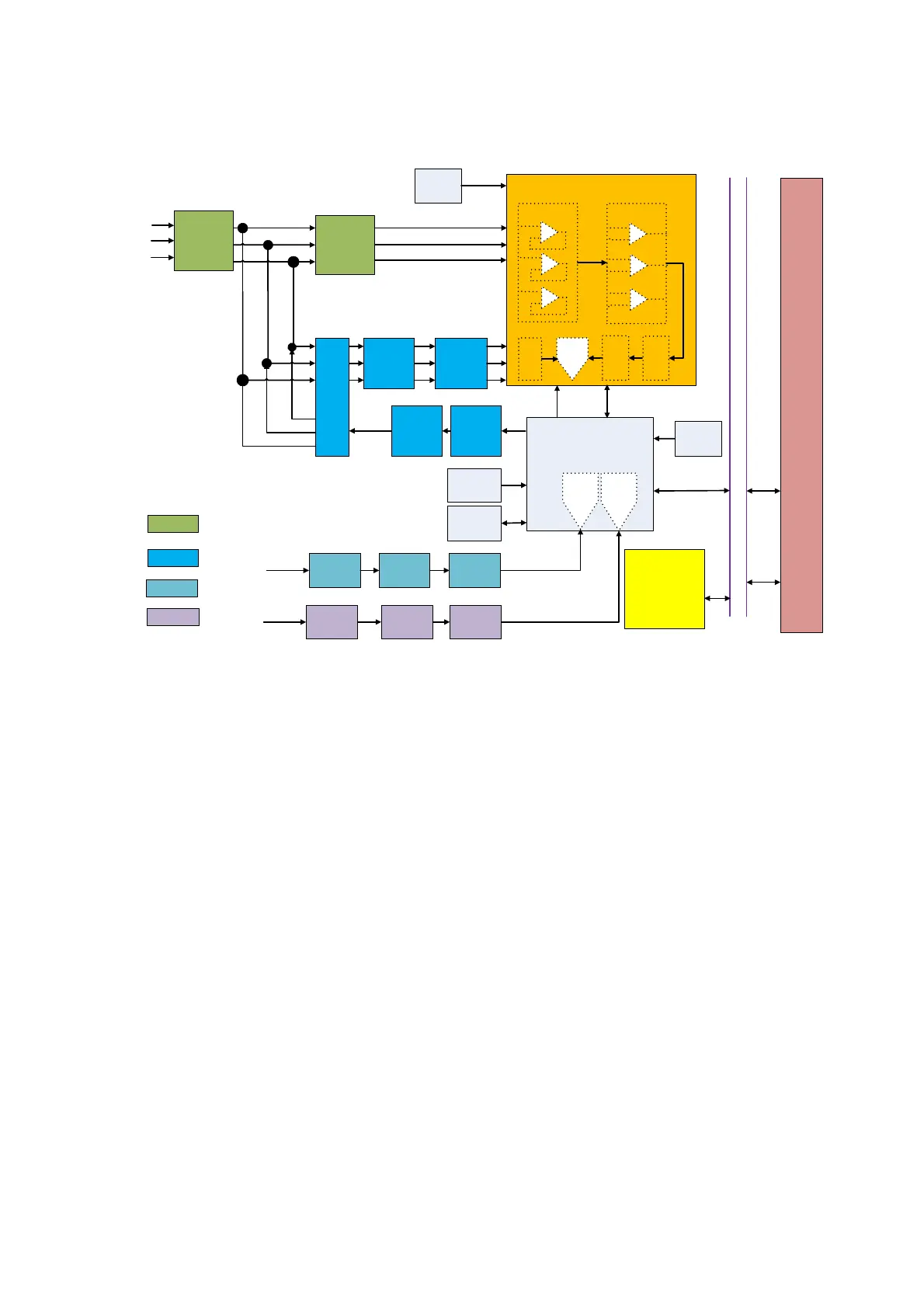

Figure 6 Principle Diagram of ECG module

The ECG module is designed for monitoring of ECG signals and display of ECG waveforms, which

serve as the reference of ultrasound images. This module can synchronously trigger display of 2-D

images and color flow images. After the ECG signal is amplified, filtered and sampled, the signal is

sent to the DSC module through the serial port; at the same time the R-wave is detected, and the

detected ECG-triggering signal is sent to the system controllers through interrupt, to start the scan

transmission.

The detail specifications are:

Support 3 lead: RA, LA and LL available.

Do not support lead reorganization.

Only support one channel.

AC overloading protection, 50Hz/60Hz, 1Vp-p, duration 10s, module return to be normal after

overload signal disappear

3 lead provides drop check of all limbs lead and RL lead.

QRS: 0.2mV.

Input impedance is more than 5 MΩ (10Hz).

The input range of ECG is ±8 mV.

Loading...

Loading...