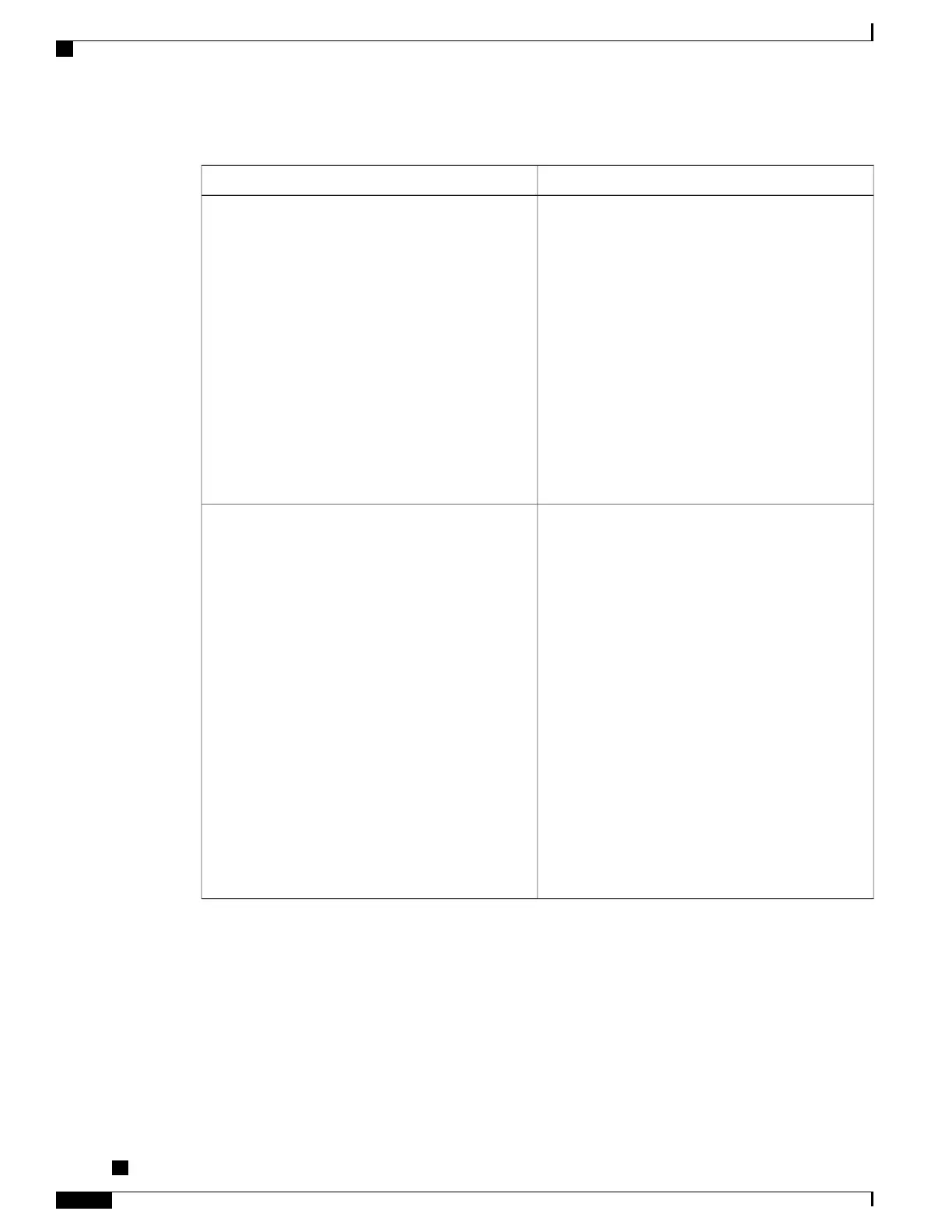

Table 48: SPA

–

Based Matrix for Ingress Classification at SIP/SPA Level

Classification at the SIP LevelClassification at the SPA Level

Serial and Channelized SPA

•

SPA-2XCT3/DS0

•

SPA-4XCT3/DS0

•

SPA-8XCHT1/E1

•

SPA-8XCHT1/E1-V2

•

SPA-1XCHSTM1/OC3

•

SPA-1XCHOC12/DS0

•

SPA-2xT3/E3

•

SPA-4xT3/E3

•

SPA-4xT-SERIAL

Ethernet SPAs

•

SPA-4X1FE-TX-V2

•

SPA-8X1FE-TX-V2

•

SPA-2X1GE-V2

•

SPA-5X1GE-V2

•

SPA-8X1GE-V2

•

SPA-10X1GE-V2

•

SPA-1X10GE-L-V2

POS SPAs

•

SPA-2XOC3-POS

•

SPA-4XOC3-POS

•

SPA-4XOC3-POS-V2

•

SPA-1XOC12-POS

•

SPA-2XOC12-POS

•

SPA-4XOC12-POS

•

SPA-8XOC12-POS

•

SPA-8XOC3-POS

•

SPA-1XOC48POS/RPR

•

SPA-2XOC48POS/RPR

•

SPA-4XOC48POS/RPR

•

SPA-OC192POS-XFP

—

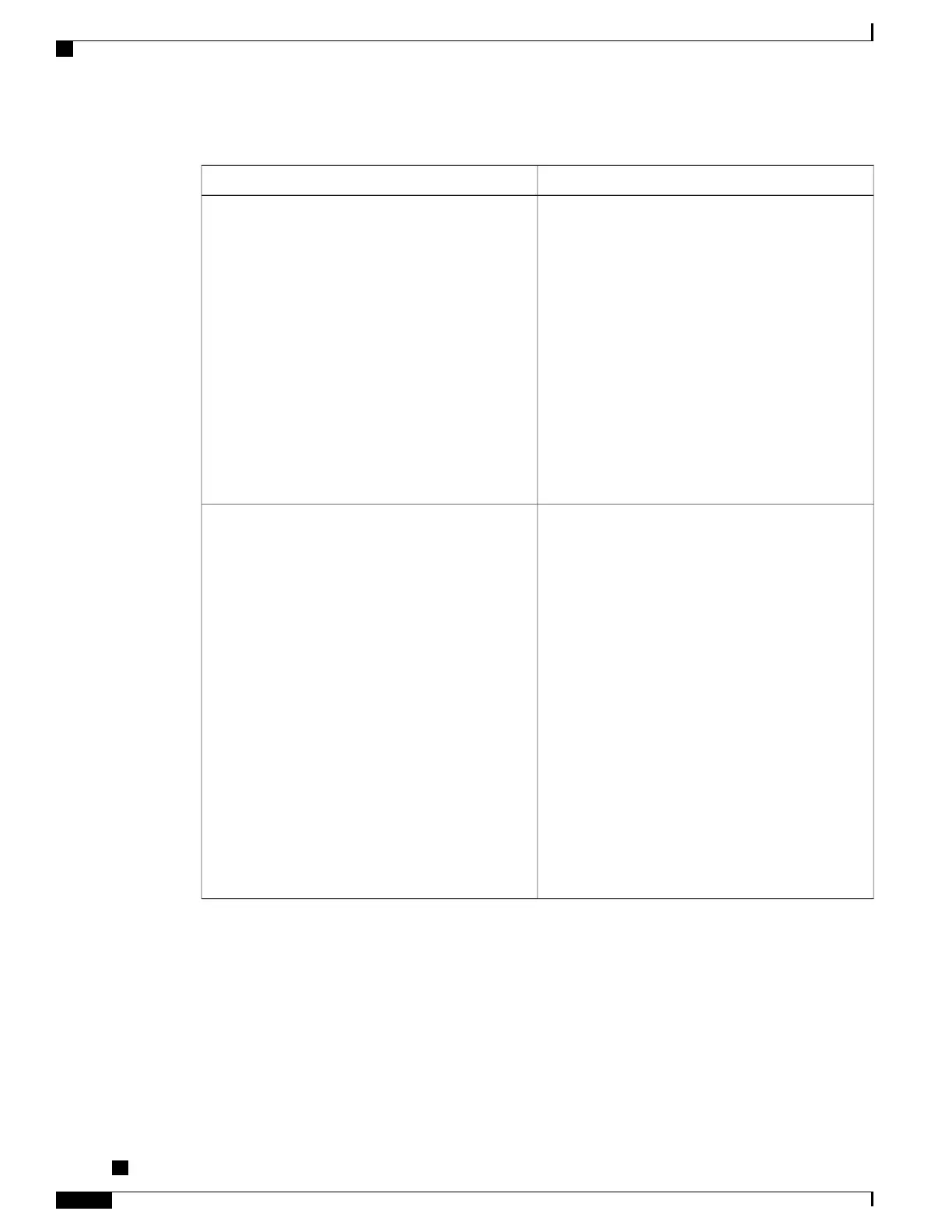

SPA-Based Classification

Ethernet and ATM SPAs perform classification at the SPA level. In the SPA-based classification model, the

SPA performs both L2 and L3 classification, and decides on the priority of the packet. After classifying the

packets into high priority and low priority, the SPA has unique SPI4 channels per priority, and all the

high-priority packets are sent on separate SPI4 channels other than the low-priority SPI4 channel. In such a

scenario, the SPA queues the packets on high SPI4 channels to high-priority buffers and low-SPI4 channels

Cisco ASR 1000 Series Aggregation Services Routers SIP and SPA Software Configuration Guide, Cisco IOS

XE Everest 16.5

438 OL-14127-17

Classifying and Scheduling Packets for the ASR 1000 Series Aggregation Services Routers

Ingress Classification Overview

Loading...

Loading...