199

Interrupt Functions Section 5-1

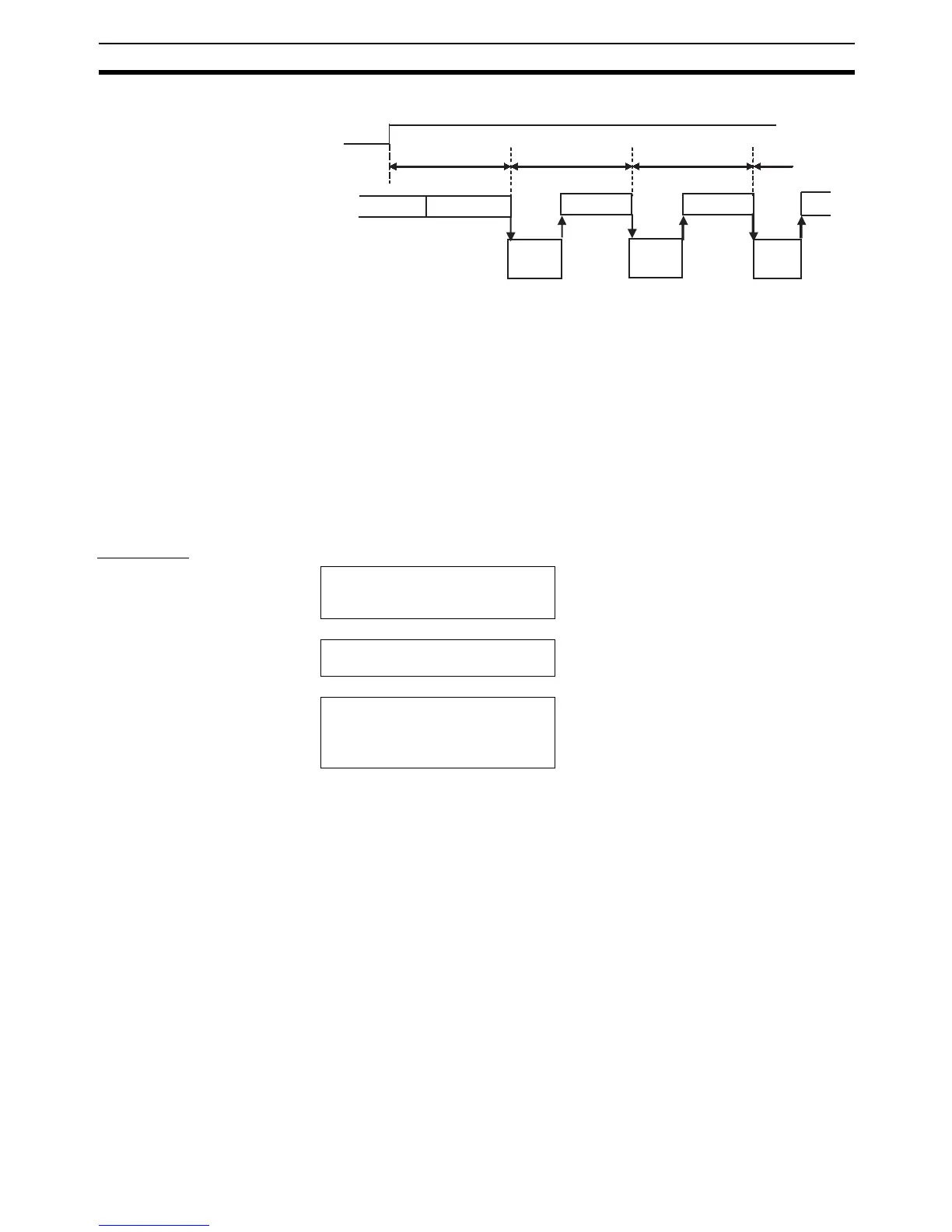

Scheduled interrupt 2 is executed every 30.5 ms.

5-1-5 High-speed Counter Interrupts

This function executes the specified interrupt task (0 to 255) when the CP1H

CPU Unit’s built-in high-speed counter PV matches a pre-registered value

(target value comparison) or lies within a pre-registered range (range compar-

ison).

• CTBL(882) is used to register the comparison table.

• Either CTBL(882) or INI(880) can be used to start comparison.

• INI(880) is used to stop comparison.

For details on the built-in high-speed counter, refer to 5-2 High-speed

Counters.

Procedure

W 0.00

30.5 ms 30.5 ms 30.5 ms

Cyclic task

processing

Interrupt

task 2

Interrupt

Interrupt

task 2

Interrupt

Interrupt

task 2

Interrupt

Cyclic task

processing

Cyclic task

processing

Cyclic task

processing

Internal

clock

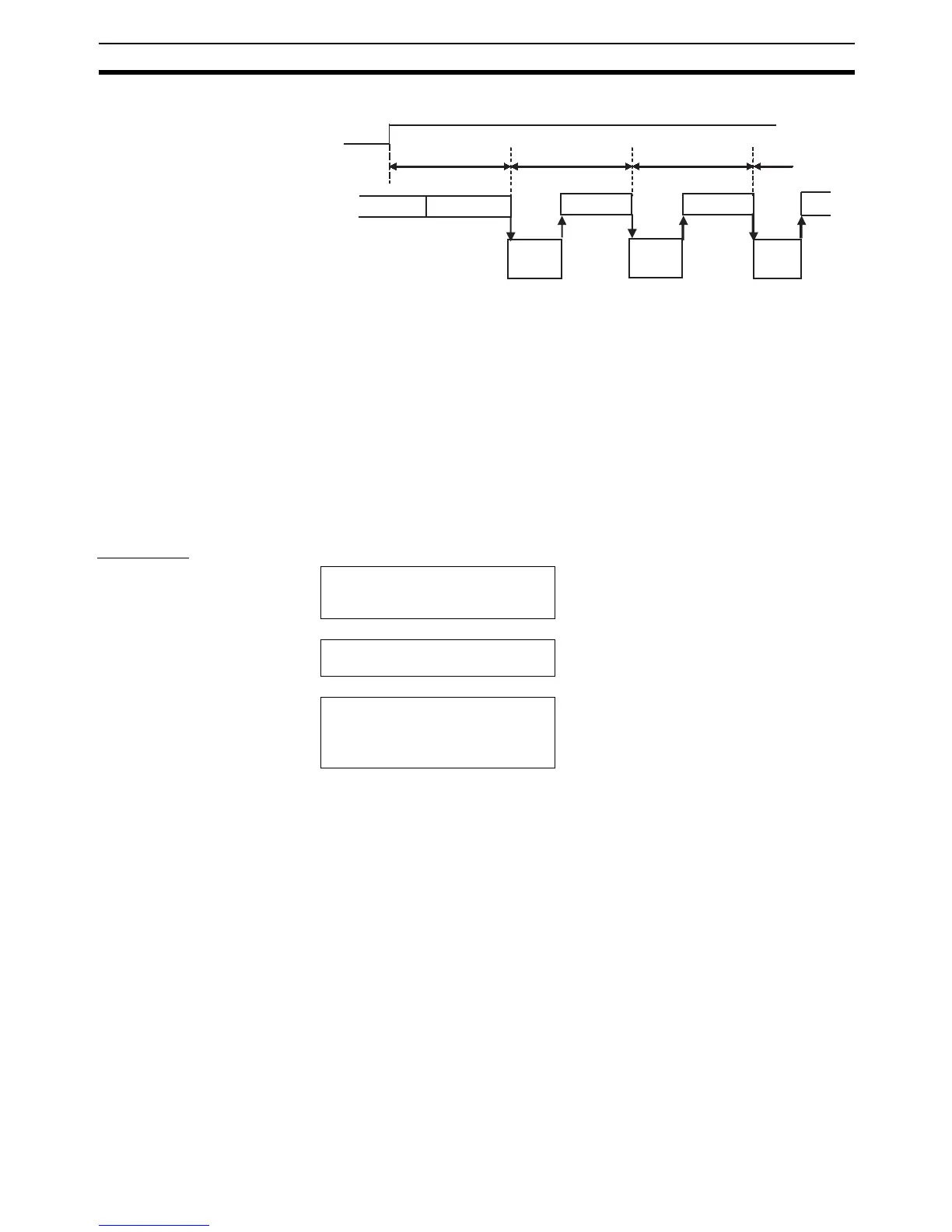

Set the PLC Setup.

• Using the CX-Programmer, set the PLC

Setup so that the built-in input is used for a

high-speed counter.

↓

Wire the inputs.

• Wire the input being used for the high-speed

counter.

↓

Write the ladder program.

• Write the interrupt task program.

• Use CTBL(882) to register the high-speed

counter number and comparison table. Cre-

ate the comparison table’s data in advance.

Loading...

Loading...