Clocks and Power Control

MOTOROLA MPC823e REFERENCE MANUAL 5-21

CLOCKS AND POWER

5

CONTROL

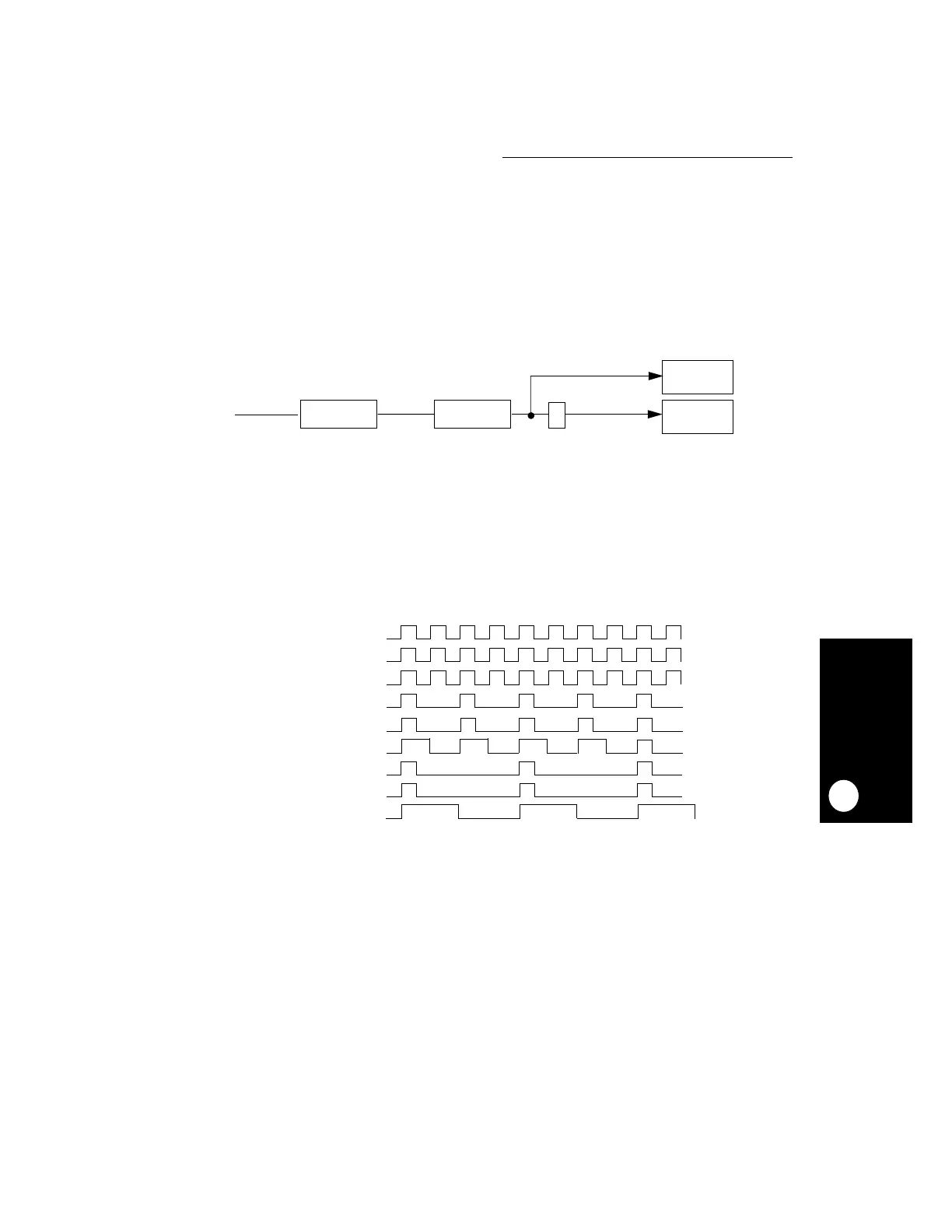

5.3.4.4 THE LCD CLOCKS. The LCD clocks—LCDCLK and LCDCLK50—are used by the

LCD controller circuitry to transfer the frame data to pixel format data. LCDCLK defaults to

VCOOUT, which is the user-defined system frequency (25-75MHz).When the PON bit in the

LCCR is set, the ratio between the system clock frequency value and the LCD clock

frequency value must be an integer value. The LCD clock frequency is the system frequency

divided by two serial dividers. LCDCLK50 is a 50% duty-cycle clock at the same frequency

as LCDCLK that is used as a clock output to the LCD panel. DFLCD and DFALCD must be

set so that the total LCD clock division factor never exceeds 64.

The LCDCLK and LCDCLK50 frequency is:

Figure 5-13. LCDCLK Divider

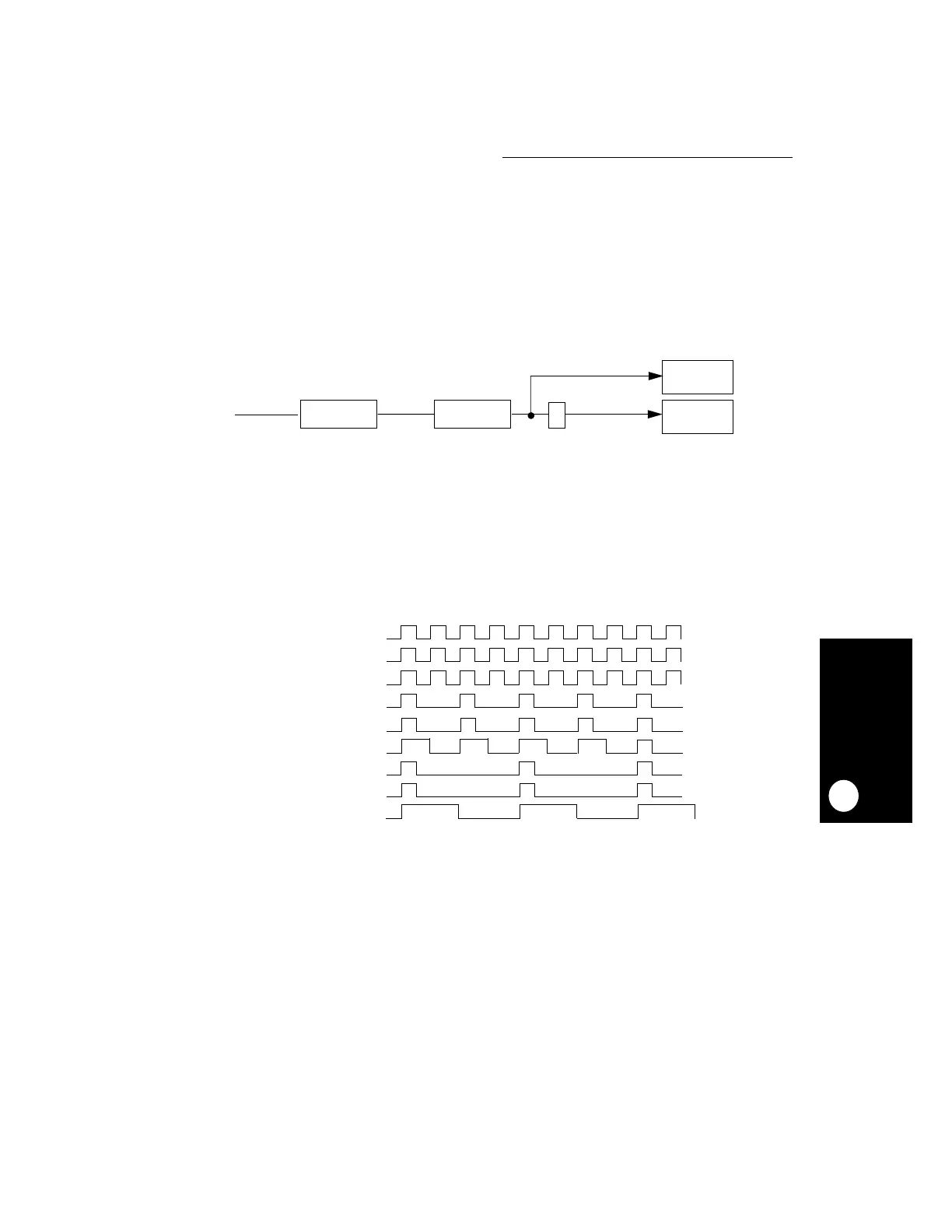

Figure 5-14. LCD Clock Timing Diagram

DFLCD DFALCD

LCD/VIDEO

CONTROLLER

LCD PANEL

LCDCLK

LCDCLK50

VCOOUT

LCDCLK

freq

=

LCDCLK50

freq

VCOOUT

freq

2

DFLCD

()

2 DFALCD + 1

×()×

--------------------------------------------------------------------------------------=

LCDCLK DIVIDE BY 1

LCDCLK50 DIVIDE BY 1

LCDCLK DIVIDE BY 2

LCDCLK50 DIVIDE BY 2

LCDCLK DIVIDE BY 4

LCDCLK50 DIVIDE BY 4

GCLK2 DIVIDE BY 1

GCLK2 DIVIDE BY 2

GCLK2 DIVIDE BY 4

Loading...

Loading...