Memory Management Unit

MOTOROLA

MPC823e REFERENCE MANUAL

11-9

MEMORY MANAGEMENT

11

UNIT

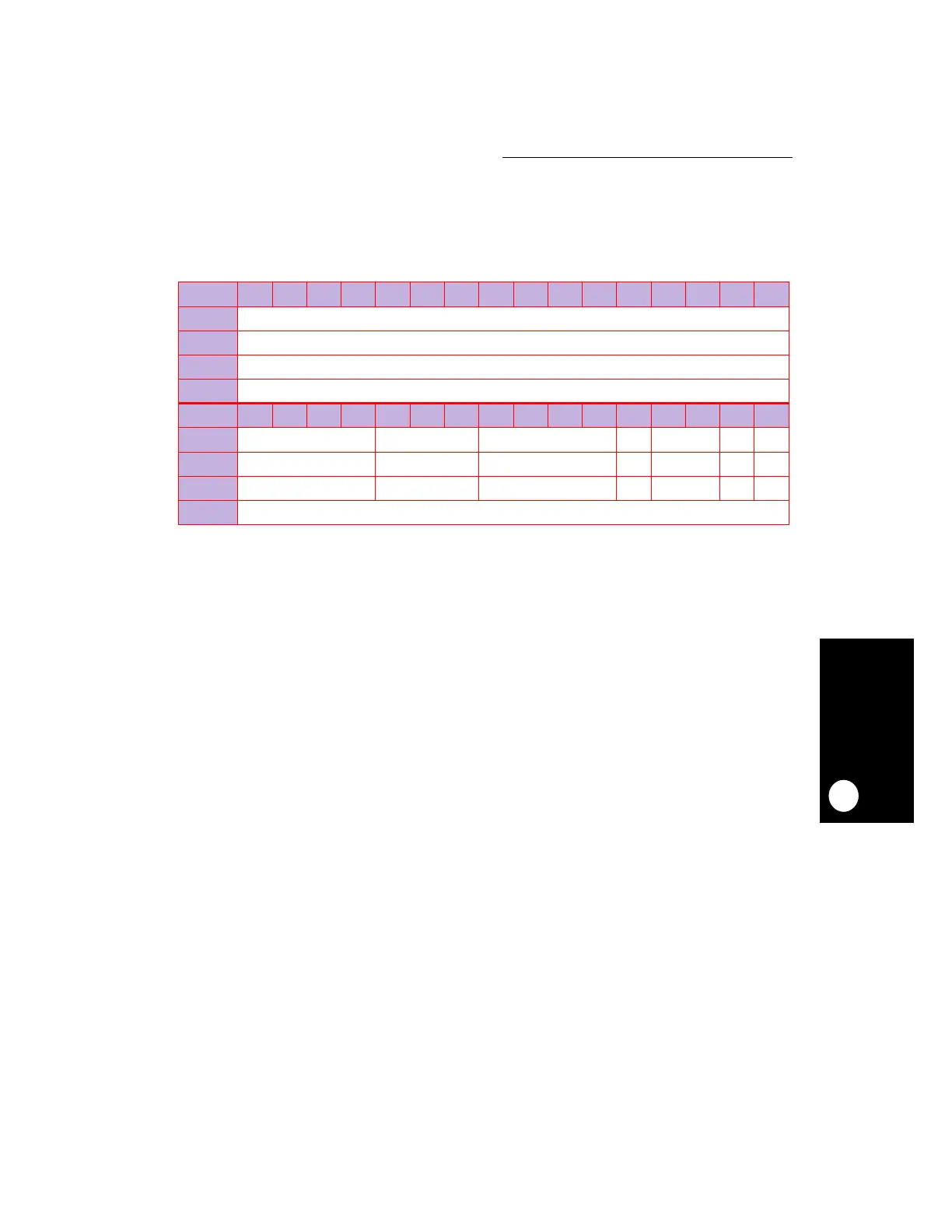

11.5.1 Level One Descriptor

The following table describes the hardware-assisted level one descriptor format that

minimizes the software tablewalk routine.

L2BA—Level 2 Table Base Address

This field contains a pointer to a base address of the level 2 table. Bits 18 and 19 are only

used when MD_CTR

TWAM

= 1. Otherwise, they must be set to 0.

Bits 20–22—Reserved

These bits are reserved and must be set to 0.

APG—Access Protection Group

This field contains access protection for the entire memory segment associated with this

entry of the table.

G—Guarded Storage Attribute for Entry

0 = Unguarded storage.

1 = Guarded storage.

PS—Page Size Level One

00 = Small (4K or 16K).

01 = 512K.

11 = 8M.

10 = Reserved.

WT—Writethrough Attribute for Entry

0 = Copyback cache policy region (default).

1 = Writethrough cache policy region.

LEVEL ONE DESCRIPTOR FORMAT

BIT

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

L2BA

RESET

—

R/W

R/W

ADDR

SYSTEM MEMORY XXXXX0000

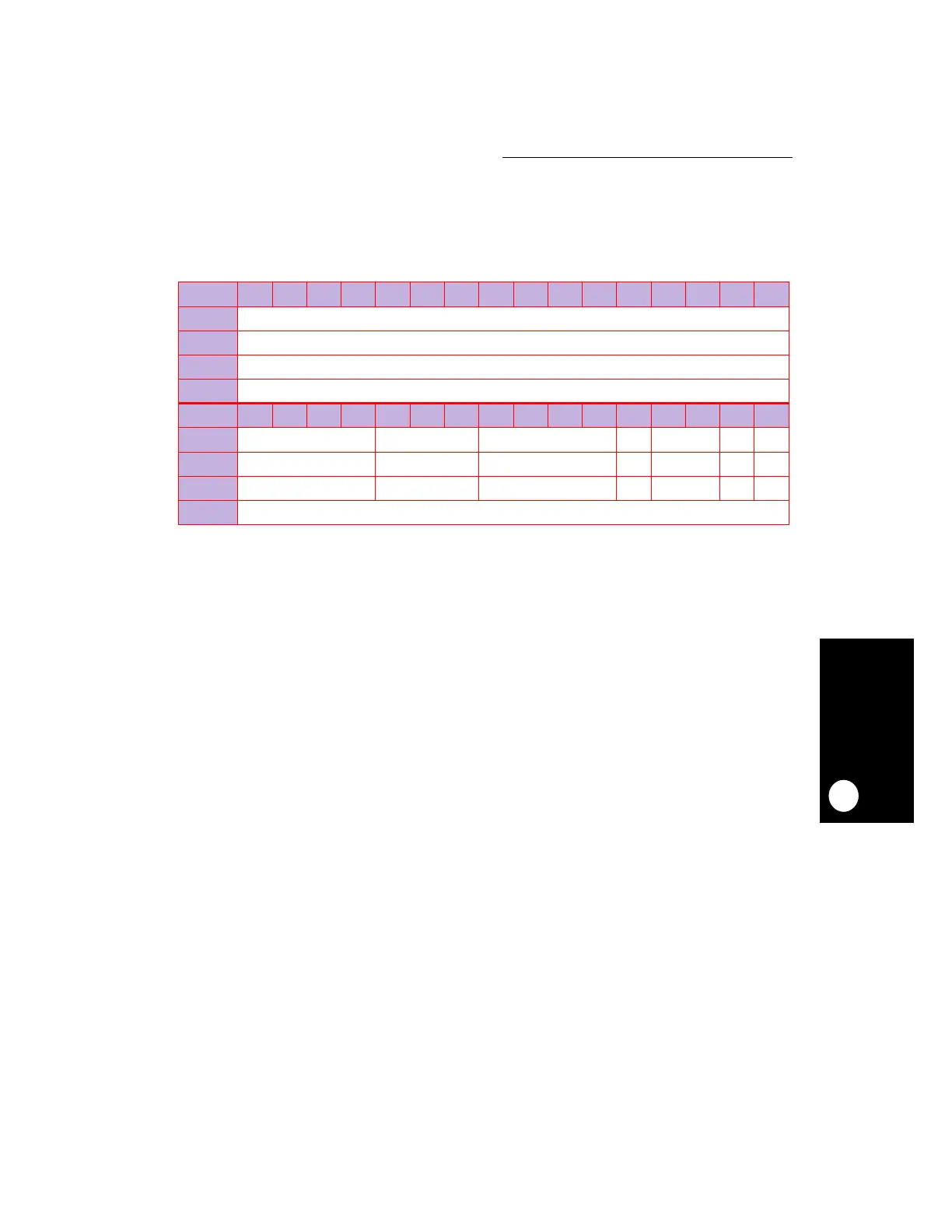

BIT

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

FIELD

L2BA RESERVED APG G PS WT V

RESET

———————

R/W

R/W R/W R/W R/W R/W R/W R/W

ADDR

SYSTEM MEMORY XXXXX002

NOTE: — = Undefined. The default values depend on the state of system memory.

Loading...

Loading...