Instruction Cache

MOTOROLA

MPC823e REFERENCE MANUAL

9-7

INSTRUCTION CACHE

9

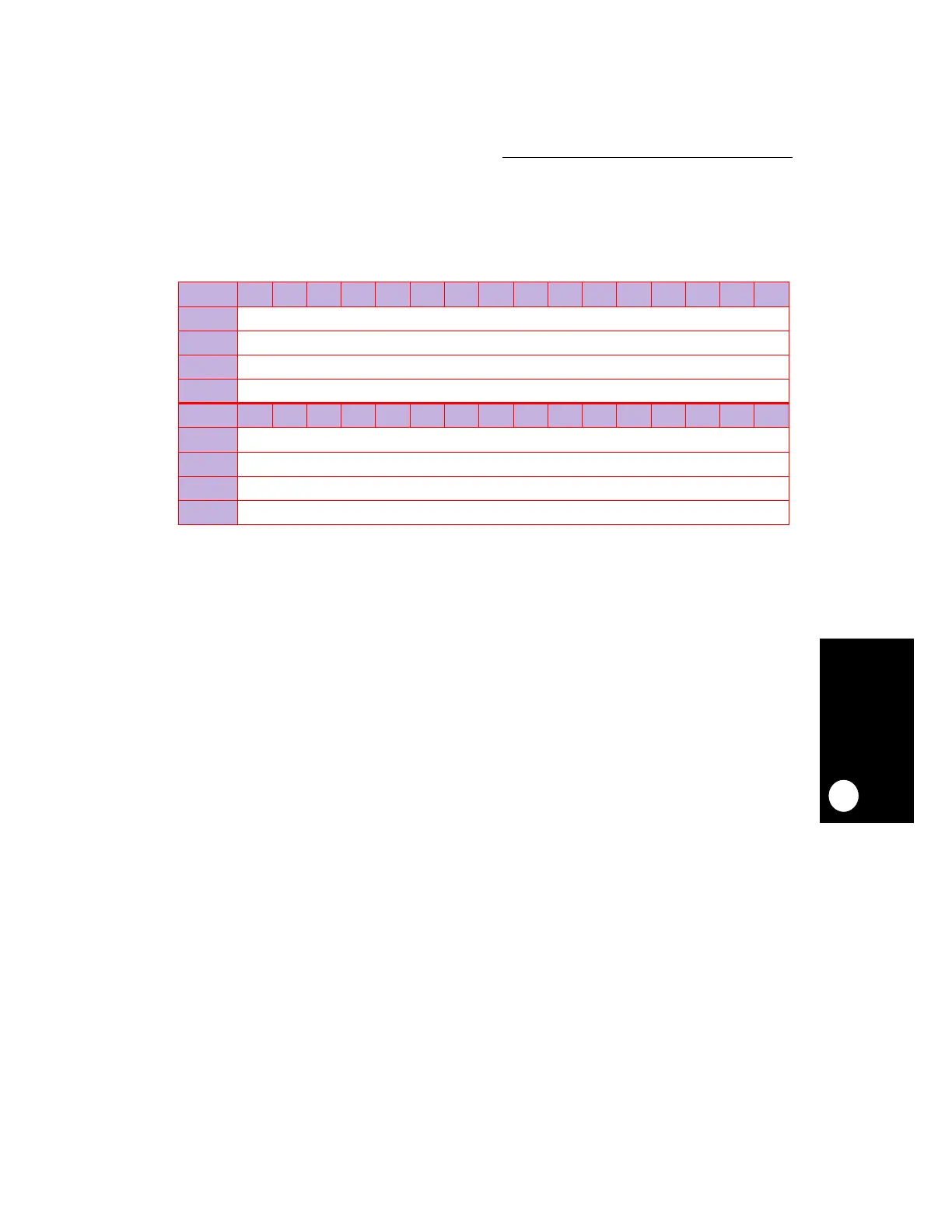

9.2.3 Instruction Cache Data Port Register

The instruction cache data port register (IC_DAT) contains data that is received from the

instruction cache.

DAT—Data

This field represents the data received when reading information from the instruction cache.

The format may vary depending on the selected cache.

9.3 INSTRUCTION CACHE OPERATION

On an instruction fetch, bits 20-27 of the instruction’s address point into the cache to retrieve

the tags and data of one set. The tags from all four accessed ways are then compared

against bits 0-19 of the instruction’s address. If a match is found and the matched entry is

valid, then it is a cache hit. If none of the tags match or the matched tag is not valid, it is a

cache miss. The instruction cache includes one burst buffer that holds the last line received

from the bus and one line buffer that holds the last line retrieved from the cache array. If the

requested data is found in one of these buffers, it can also be considered a cache hit. Refer

to Figure 9-2 for more information. To minimize power consumption, the instruction cache

attempts to make use of data stored in one of its internal buffers. Using a special indication

from the core, it is possible to make sure that the requested data is in one of the buffers early

enough that the cache array is not activated.

9.3.1 Instruction Cache Hit

When a cache hit occurs, bits 28-29 of the instruction address are used to select one word

from the cache line whose tag matches the instruction pointer. The instruction is then

immediately transferred to the instruction unit of the core.

IC_DAT

BIT

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

DAT

RESET

—

R/W

R/W

SPR

562

BIT

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

FIELD

DAT

RESET

—

R/W

R/W

SPR

562

NOTE: — = Undefined.

Loading...

Loading...