Clocks and Power Control

5-22

MPC823e REFERENCE MANUAL

MOTOROLA

CLOCKS AND POWER

5

CONTROL

5.3.5 Clock Configuration

You can configure the clock of the MPC823e using the MODCK1 and MODCK2 pins. The

SPLL has several power and ground pins (VDDSYN, VSSSYN, VSSSYN1, and XFC) that

must be properly terminated for stability and CLKOUT integrity.

5.3.5.1 MODE CLOCK PINS.

The MODCK1 and MODCK2 pins are used to determine

clock source and configuration options. These pins are sampled on the rising edge of the

PORESET

pin. MODCK1 specifies the input source to the SPLL and, combined with

MODCK2, specifies the multiplication factor at reset. If you do not want the PITRTCLK,

TMBCLK, and multiplication factor to change during power-down mode, do not sample the

MODCK1 and MODCK2 pins during wake-up. Thus, the PORESET

pin must remain

negated while the HRESET

pin is asserted during this wake-up sequence.

MODCK1 selects the clock source to use (EXTCLK or main oscillator) and MODCK2 selects

the reference frequency (4MHz, 32kHz, or EXTCLK). If, during the power-on reset

sequence, the MODCK1 pin is zero, then the oscillator’s 4MHz or 32kHz clock is the

selected input. If MODCK1 is one, then the EXTCLK pin is the input source to the SPLL. The

system clock frequency (GCLK1) can be divided as defined by the DFNH and DFNL fields

in the SCCR. The maximum system clock frequency occurs when the DFNH field is equal

to 00. If MODCK2 is zero during the power-on reset sequence, the input frequency is either

32kHz or EXTCLK (one-to-one mode). If the MODCK2 pin is one, then a 4MHz clock is the

input source to the SPLL.

If the EXTCLK pin is the main timing reference and the OSCM is the timing reference to the

real-time clock and periodic interrupt timer, then the frequency of the OSCM must be 32.768

or 38.4kHz. Depending on how the TBS bit is set in the SCCR, the timebase clock is either

the SPLL clock frequency or GCLK2. The RTSEL field in the SCCR specifies the source

(EXTCLK or OSCM) of the periodic interrupt timer and real-time clock. The RTDIV field in

the SCCR specifies the division factor (

÷

by 4 or

÷

by 512).

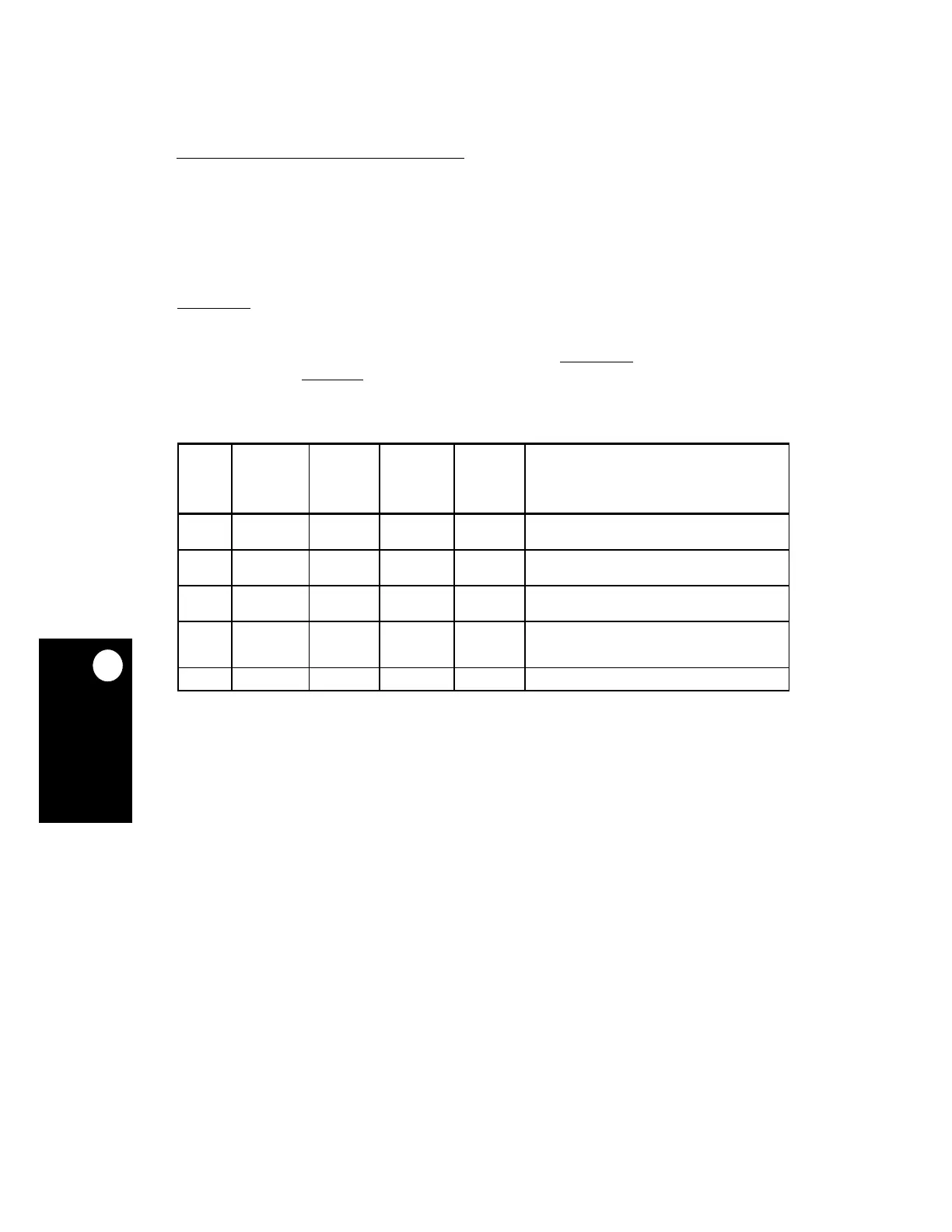

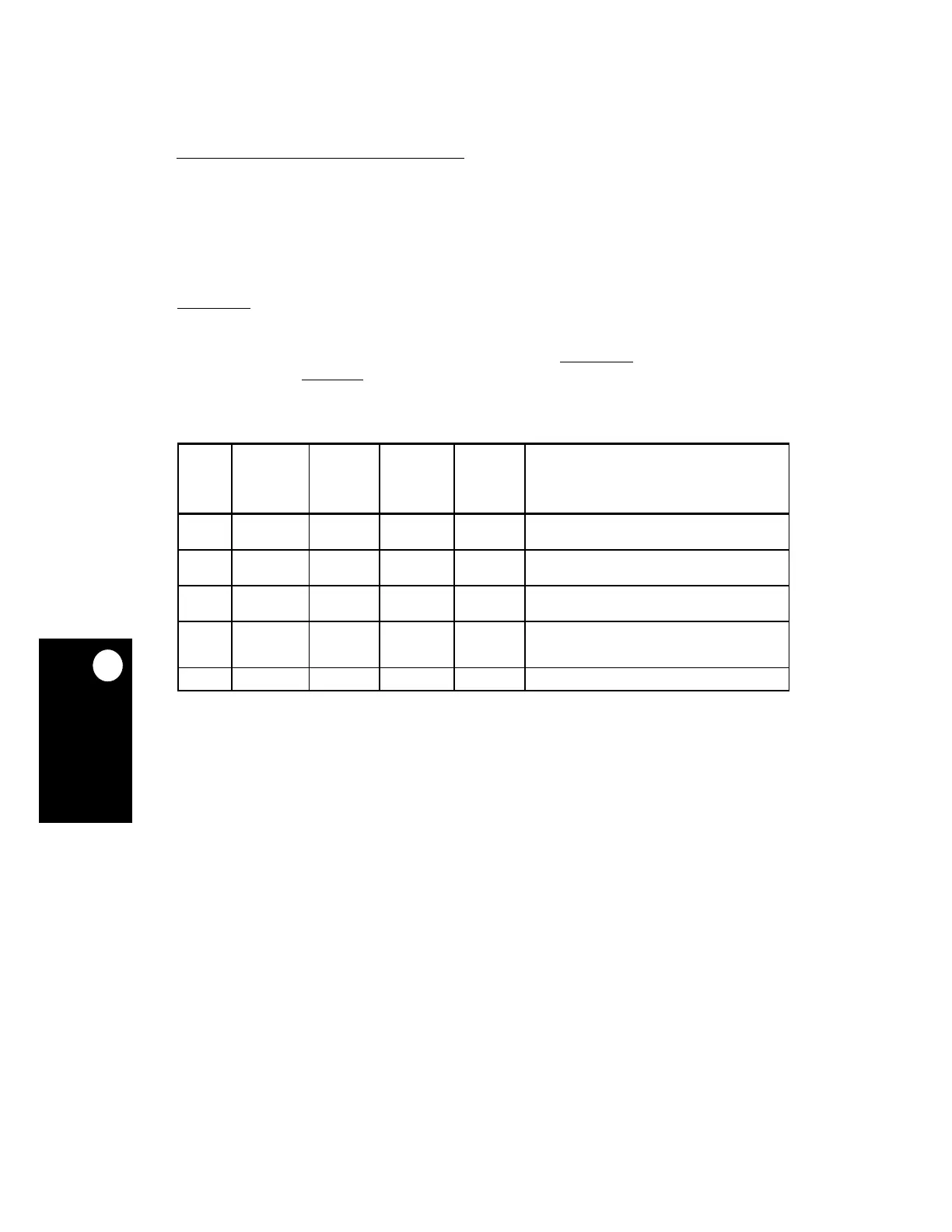

Table 5-2. Reset Clock Source Configuration

MODCK

[1:2]

POWER-ON

RESET

(POR)

DEFAULT

MF + 1

AT POR

PITRTCLK

DIVISION

DEFAULTS

AT POR

TMBCLK

DIVISION

DEFAULTS

AT POR

SPLL OPTIONS

00 0 513 4 4 Normal operation, SPLL enabled.

Main timing reference is OSCM

freq

= 32 kHz.

01 0 5 512 4 Normal operation, SPLL enabled.

Main timing reference is OSCM

freq

= 4 MHz.

11 0 5 512 4 Normal operation, SPLL enabled.

Main timing reference is EXTCLK

freq

= 4 MHz.

10 0 1 512 16 Normal operation, SPLL enabled.

One-to-one Mode, Maximum

OSCM

freq

= EXTCLK

freq

— 1 — — — The configuration remains unchanged.

Loading...

Loading...