Instruction Execution Timing

MOTOROLA

MPC823e REFERENCE MANUAL

8-5

INSTRUCTION EXECUTION

8

TIMING

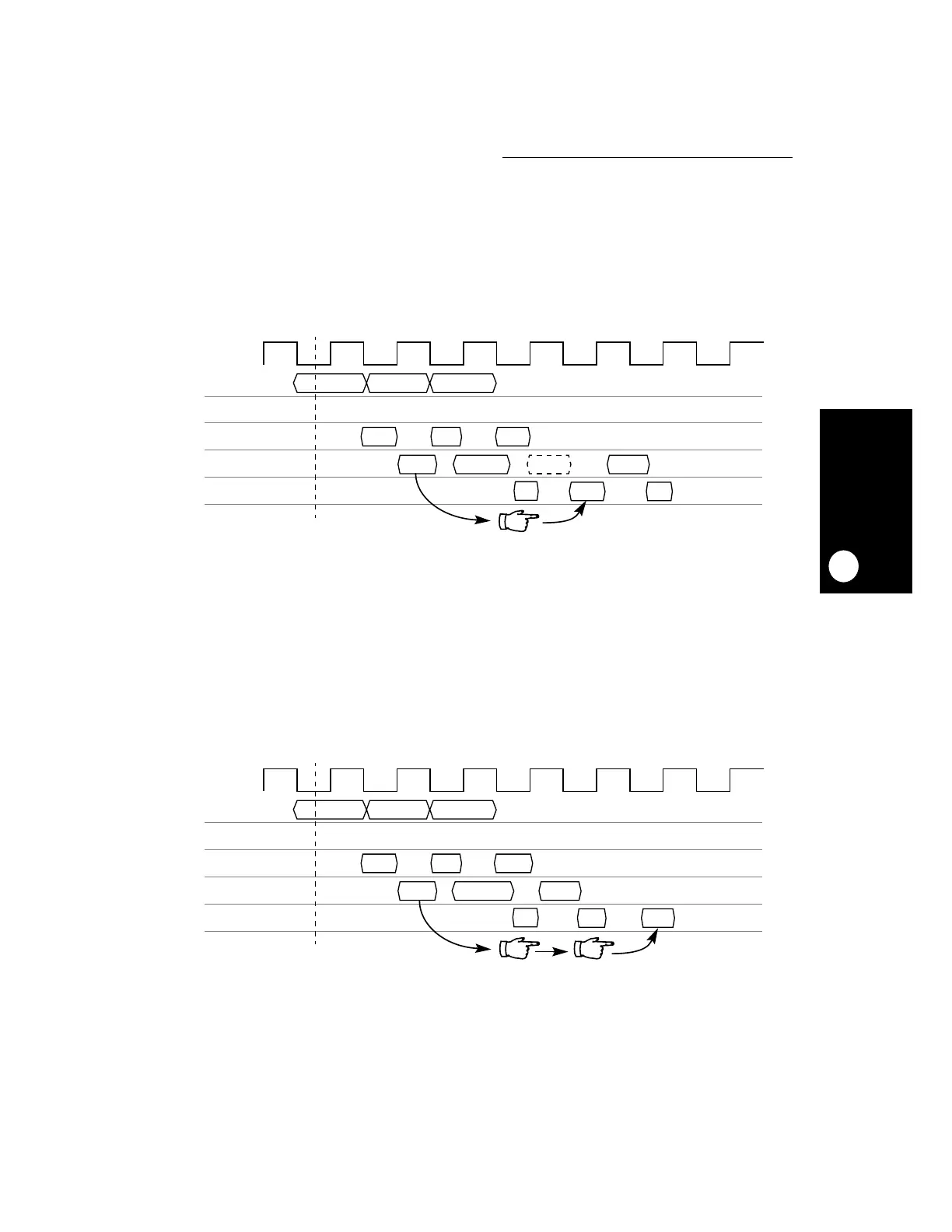

8.2.2 Writeback

8.2.2.1 WRITEBACK ARBITRATION

mulli

r12,r4,3

sub

r3,r15,3

addic

r4,r12,1

The

addic

instruction is dependent on the

mulli

result. Since the single-cycle instruction

sub

has priority on the writeback bus over the

mulli

and

the

mulli

writeback is delayed one

clock and causes a bubble in the execute stream.

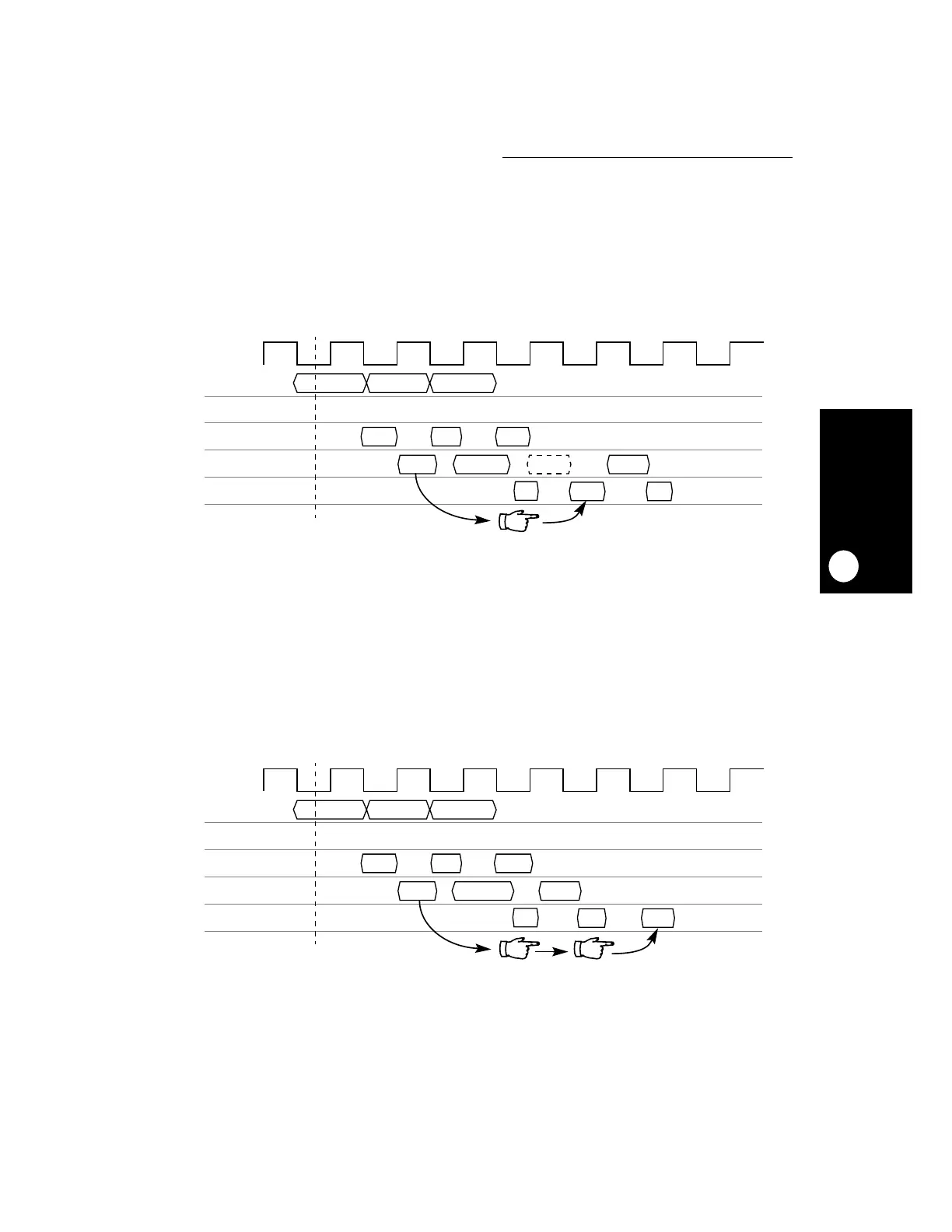

mulli

r12,r4,3

sub

r3,r15,3

addic

r4,r3,1

Figure 8-2. Example of a Writeback Arbitration

Figure 8-3. Another Example of a Writeback Arbitration

MULLI SUB ADDIC

FETCH

DECODE

READ + EXECUTE

WRITEBACK

MULLI SUB

BUBBLE

ADD

ADDIC

MULLI SUB, MULLI

MULLI

ADDIC

SUB

GCLK1

MULLI SUB ADDIC

FETCH

DECODE

READ + EXECUTE

WRITEBACK

MULLI SUB

ADD

ADDIC

MULLI SUB, MULLI

MULLI

ADDIC

SUB

GCLK1

Loading...

Loading...