Clocks and Power Control

5-24

MPC823e REFERENCE MANUAL

MOTOROLA

CLOCKS AND POWER

5

CONTROL

5.4 POWER CONTROL

To preserve the life of your battery, the MPC823e provides low-power modes that limit the

operation to essential modules. In addition to normal high mode, the MPC823e supports

normal low, doze high, doze low, sleep, deep-sleep, and power-down modes. When the

communication processor module is idle, it uses its own power-saving mechanism to shut

down automatically. There are a variety of modules connected to separate power rails that

allow you to achieve the best performance using the least amount of power.

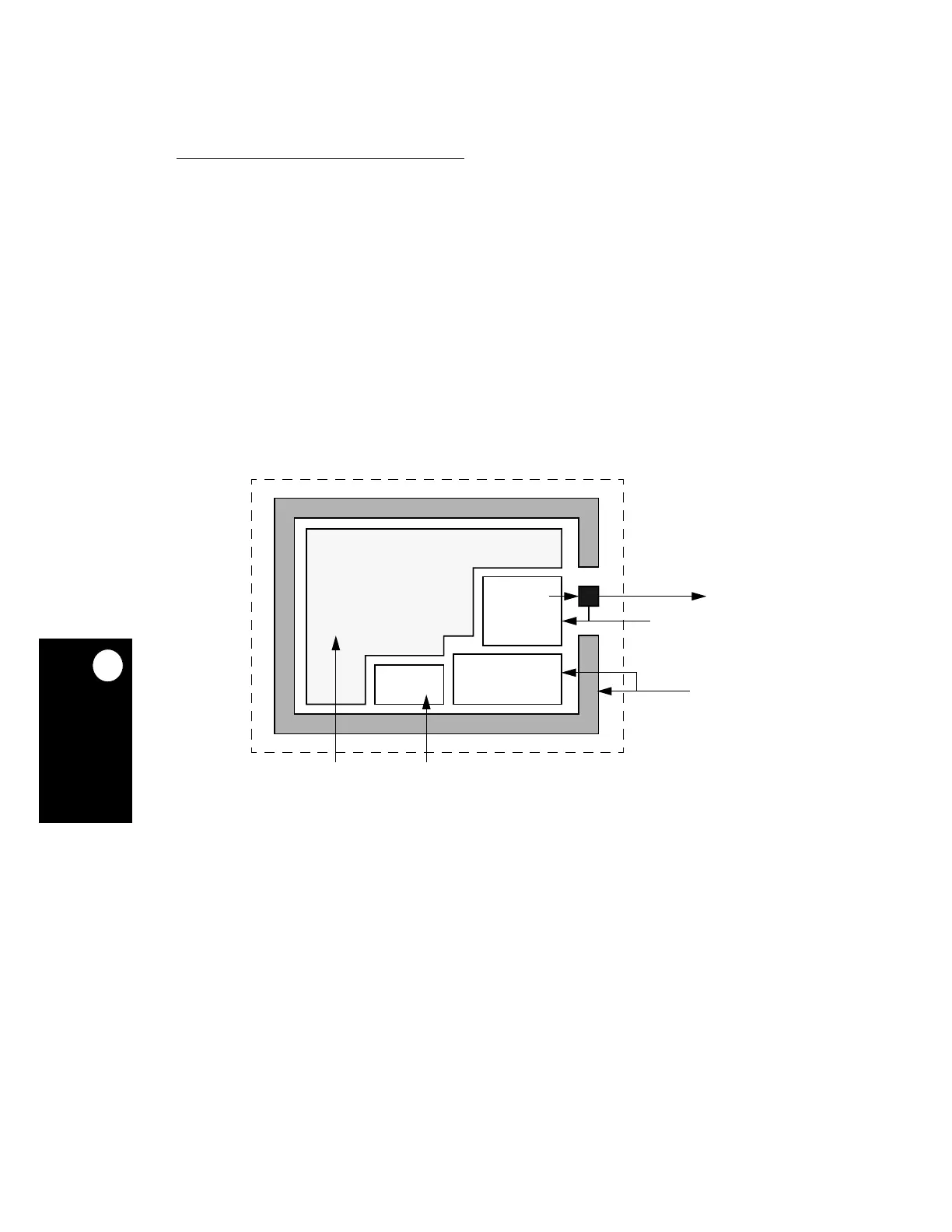

5.4.1 Power Rails

There are different power planes (called power rails) within the MPC823e that can be

connected to different power sources. Your system implementation defines the power

source for each of these different power rails. Figure 5-15 shows you which module is

connected to each power rail.

The I/O buffers, logic, and clock control are fed by a 3.3V (±5%) power supply. The internal

logic can be fed by a 3.3V source. To improve CLKOUT stability, the SPLL requires a

separate 3.3V source (VDDSYN). The OSCM, timebase, decrementer, periodic interrupt

timer, real-time clock, SCCR, PLPRCR, and RSR are all connected to the keep-alive power

(KAPWR) rail. This power rail architecture allows you to remove the power at the VDDH/

VDDL/VDDSYN pins during sleep, deep-sleep, or power-down mode. The external power

supply unit can use the TEXP pin, which is fed by the KAPWR rail, to switch between power

sources.

MPC823e

Figure 5-15. MPC823e Power Rails and TEXP Status

CLOCK CONTROL

ANALOG

PIT, RTC, TB,

DEC, SCCR,

INTERNAL LOGIC

VDDH

I / O PAD

VDDL

VDDSYN

KAPWR

TEXP

OSCM,

PLPRCR,

AND RSR

AND CLOCK DRIVERS

AND DIGITAL SPLL

SPLL

Loading...

Loading...