Clocks and Power Control

MOTOROLA

MPC823e REFERENCE MANUAL

5-25

CLOCKS AND POWER

5

CONTROL

All other circuits are powered by the normal supply pins—VDDH and VDDL—and VSS.

VDDH feeds the I/O buffers and logic and VDDL supplies the internal chip logic to reduce

system power consumption. However, the power supply connected to VDDH must be larger

or equal to the one connected to VDDL. The power supply for each block is listed in Table 5-

5 and described in

Section 5.4 Power Control

.

The following are the power supply requirements of the MPC823e:

• VDDH = VDDSYN = 3.3V

±

5%

• VDDH

≥

VDDL

≥

3.3V

±

5%

• VDDH

≥

KAPWR

≥

VDDH – 0.4V for normal operation

• KAPWR

≥

2.5V

±

5% in power-down mode

5.4.2 Keep-Alive Power

When the MPC823e is in normal operation mode, the keep-alive power supply (KAPWR) is

powered to the same voltage value as that of the I/O buffers and logic. Therefore, if the

VDDL and VDDH is 3.3V, then the KAPWR is 2.9V to 3.3V.

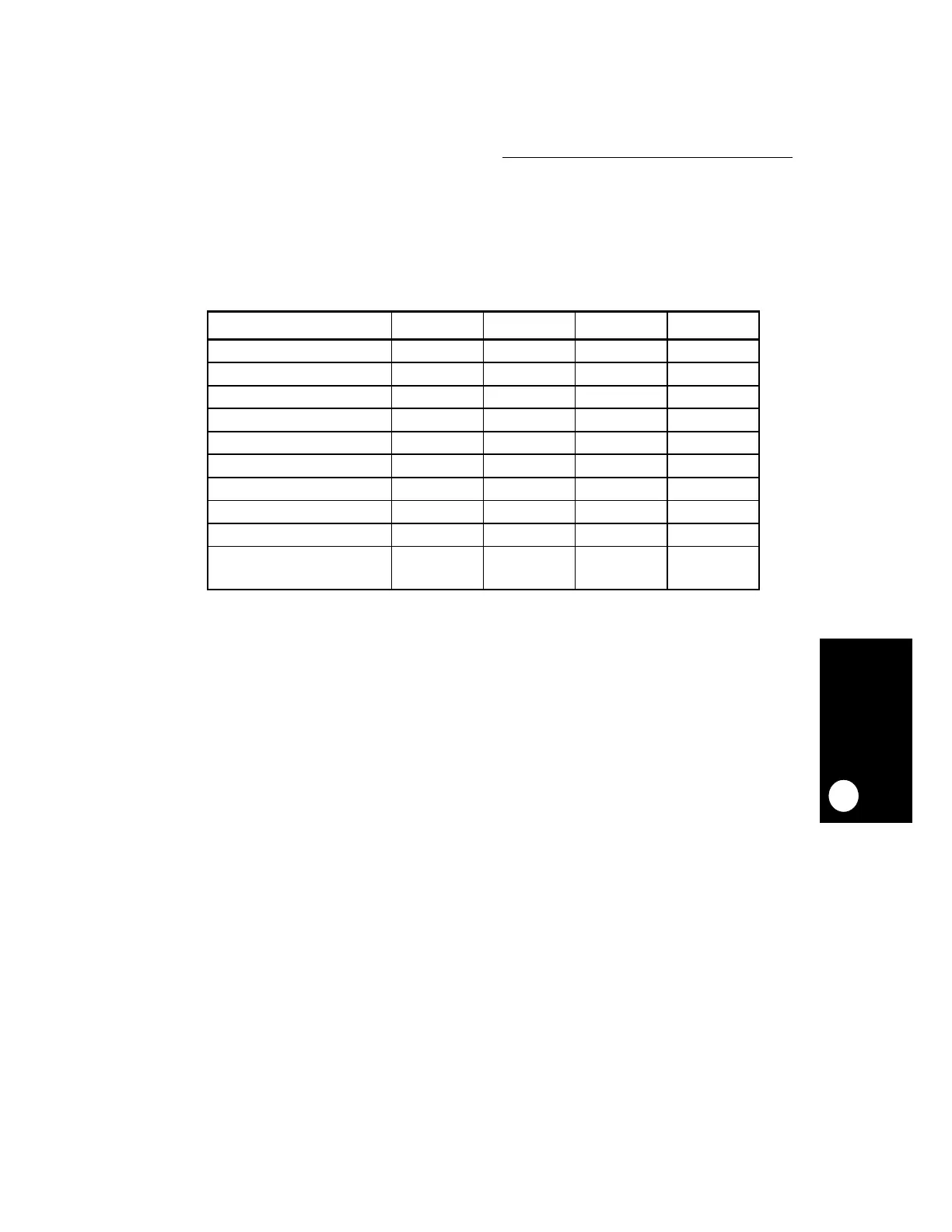

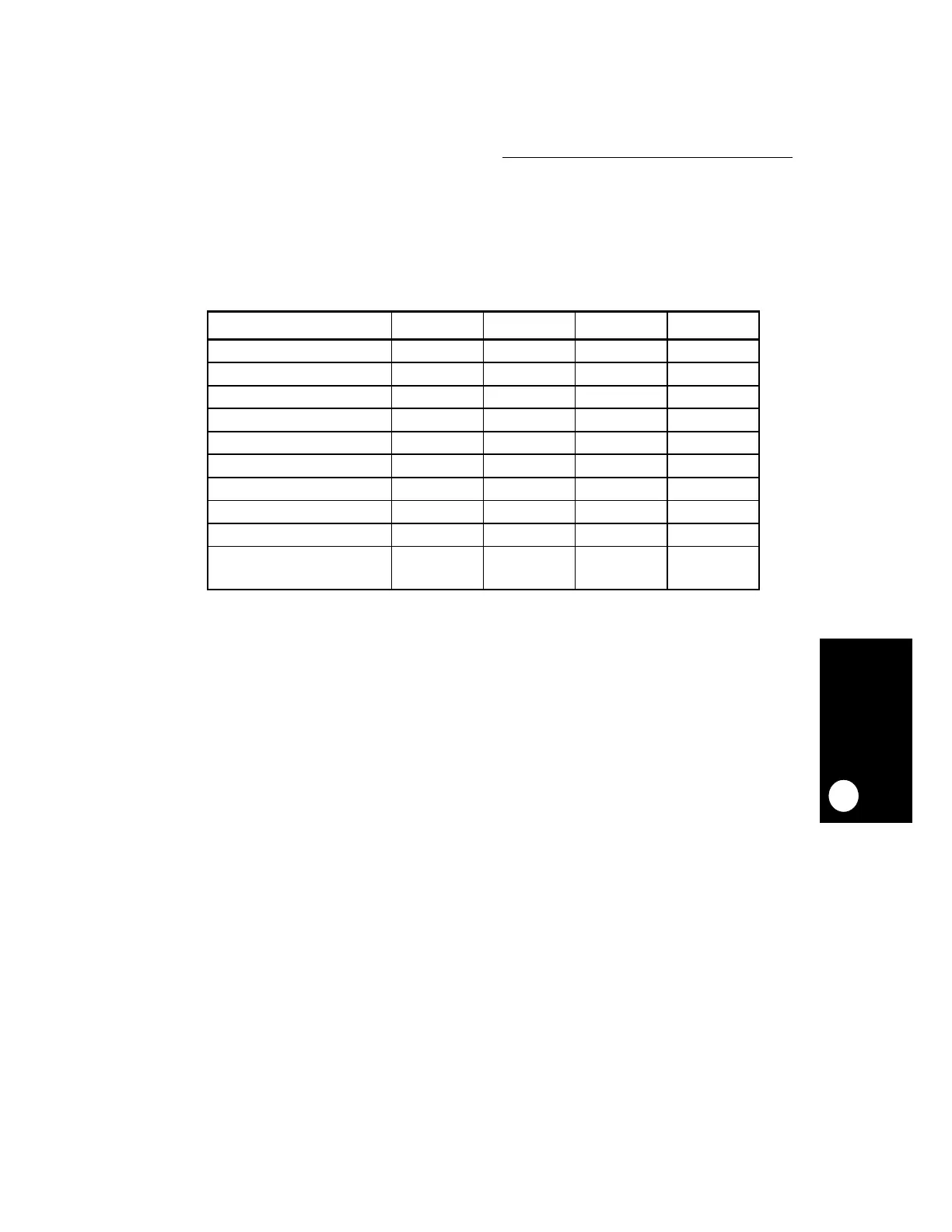

Table 5-5. MPC823e Power Supply

BLOCK VDDH VDDL VDDSYN KAPWR

I/O Pad X

CLKOUT X

Digital SPLL X

Clock Control X X

Internal Logic X

Clock Drivers X

Analog SPLL X

Main Clock Oscillator X

SCCR, PLPRCR, and RSR X

Real-Time Clock, Periodic

Interrupt Timer, Timebase and

Decrementer

X

Loading...

Loading...