System Interface Unit

12-14

MPC823e REFERENCE MANUAL

MOTOROLA

SYSTEM INTERFACE UNIT

12

12.6 THE POWERPC TIMEBASE

The timebase is defined by the PowerPC architecture and is a 64-bit free-running binary

counter that is incremented at a frequency determined by each implementation of the

timebase. There is no interrupt or other indication generated when the count rolls over. The

period of the timebase depends on the driving frequency. For the MPC823e, the timebase

is clocked by the TMBCLK clock and the period for the timebase is:

The state of the timebase is unaffected by any resets and must be initialized by the software.

Reads and writes of the timebase are restricted to special instructions. For the MPC823e

implementation, it is not possible to read or write the entire timebase in a single instruction.

Therefore, the

mttb

and

mftb

instructions are used to move the lower half of the timebase

while the

mttbu

and

mftbu

instructions are used to move the upper half of the timebase.

The timebase has two reference registers associated with it. A maskable interrupt is

generated when the timebase count reaches the value programmed in one of the two

reference registers and the two status bits indicate which of the two reference registers

generated the interrupt.

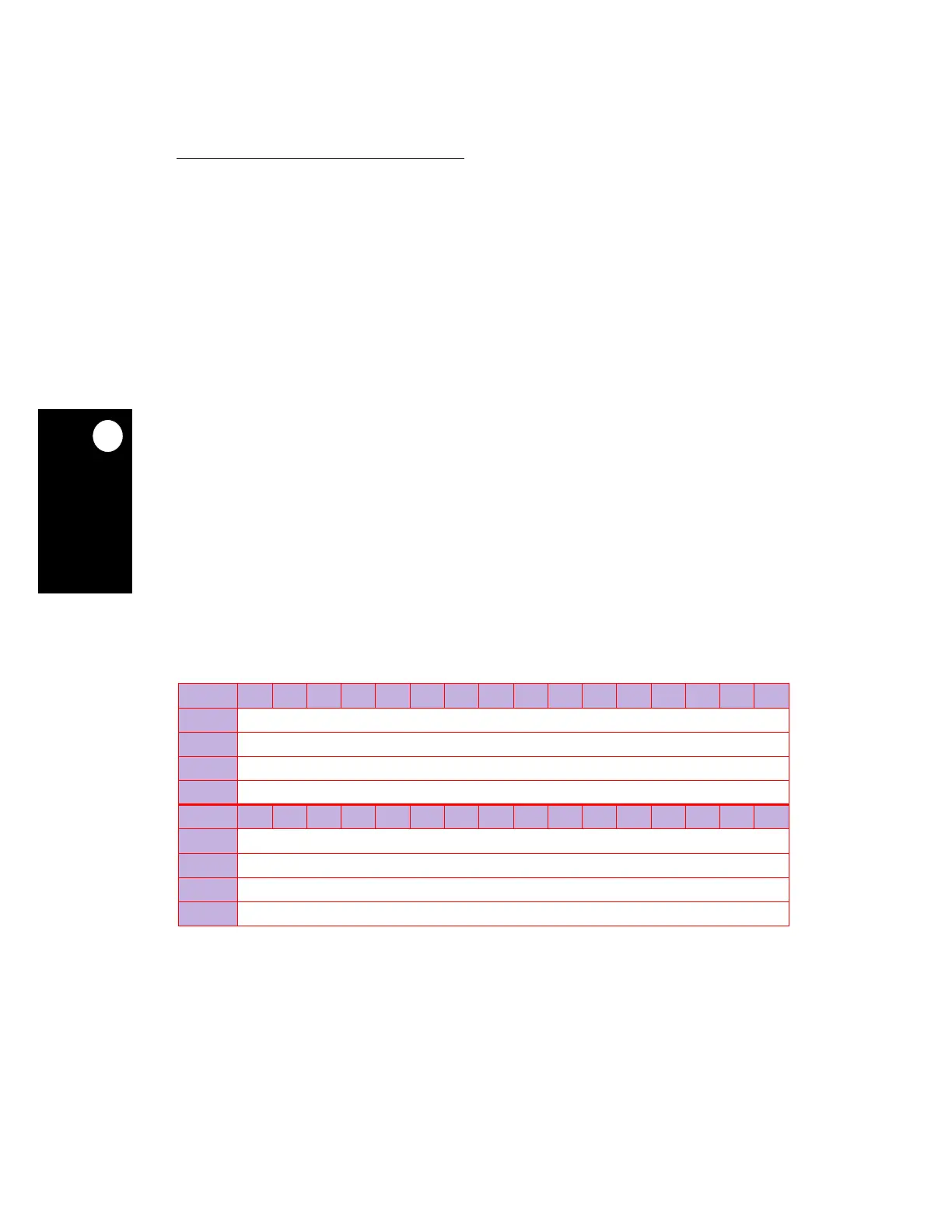

12.6.1 Timebase Register

The special-purpose 64-bit timebase (TB) register contains a 64-bit integer that is

periodically incremented. There is no automatic initialization of this register. The system

software must perform the initialization. The contents of the register can be written by the

mtspr

instruction and read by the

mftb

or

mftbu

instruction.

TBU—Timebase Upper

The value stored in this field is used as an upper part of the timebase counter.

TB-UPPER

BIT

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

TBU

RESET

—

R/W

R/W

SPR

269 (READ), 285 (WRITE)

BIT

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

FIELD

TBU

RESET

—

R/W R/W

SPR 269 (READ), 285 (WRITE)

NOTE: — = Undefined.

T

TB

2

64

F

tmbclk

-----------------------=

Loading...

Loading...