System Interface Unit

12-6

MPC823e REFERENCE MANUAL

MOTOROLA

SYSTEM INTERFACE UNIT

12

Notice that the core takes the system reset interrupt when a nonmaskable interrupt is

asserted and the external interrupt when any other interrupt is asserted by the interrupt

controller. Each one of the external IRQx

pins has its own dedicated assigned priority level

and there are eight additional interrupt priority levels. Each one of the system interface unit

internal interrupt sources (the interrupt request that is generated by the communication

processor module’s interrupt controller) can be assigned by the software to any one of those

eight interrupt priority levels. Thus, a very flexible interrupt scheme is realized.

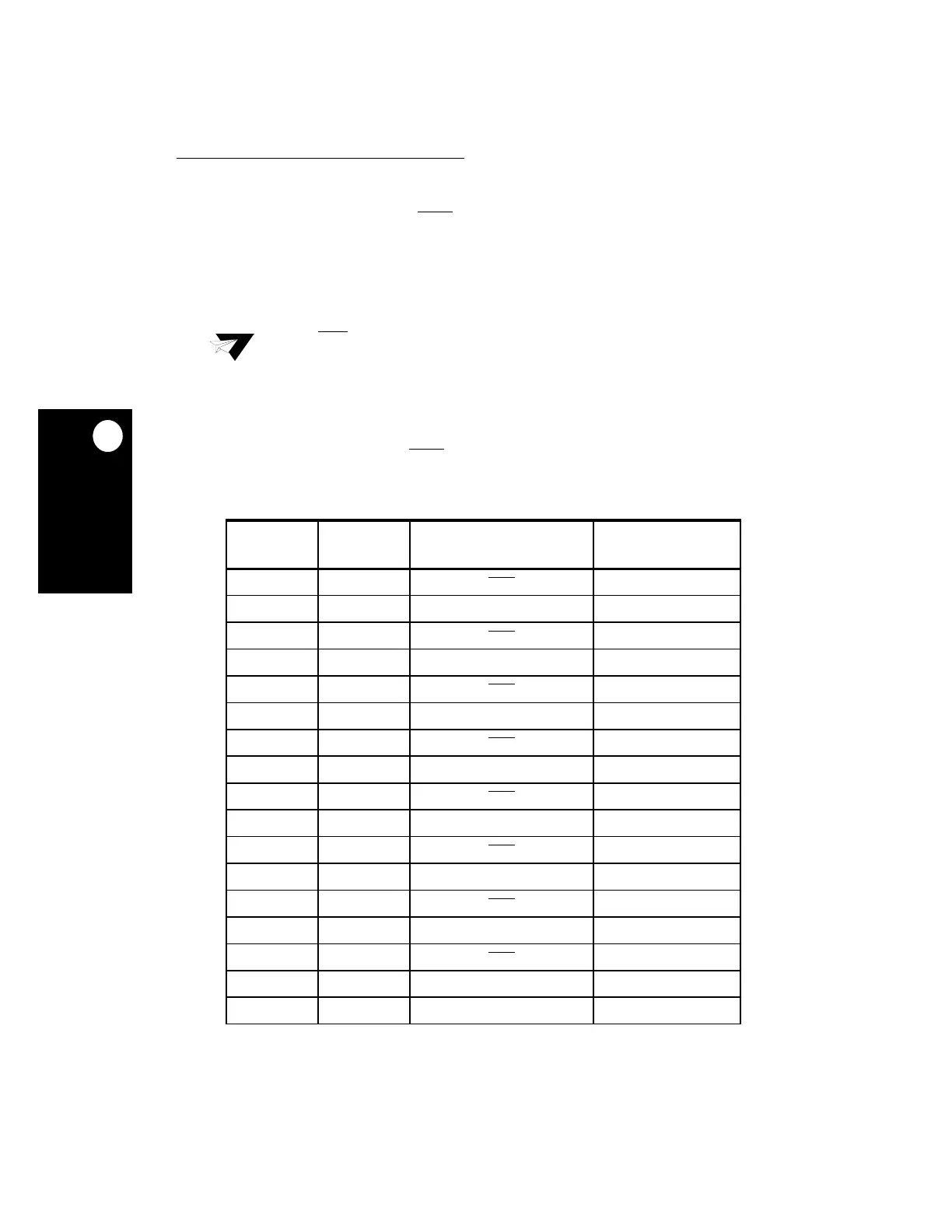

12.3.2 Priority of the Interrupt Sources

The system interface unit has 15 interrupt sources that assert just one interrupt request to

the core. There are seven external IRQx

pins and eight interrupt levels. The priority between

all interrupt sources is shown in Table 12-1.

Note:

IRQ0

is a

nonmaskable

interrupt. It will cause the core to go to the system reset

vector.

Table 12-1. Priority of System Interface Unit Interrupt Sources

NUMBER PRIORITY

LEVEL

INTERRUPT SOURCE

DESCRIPTION

INTERRUPT CODE

0 Highest IRQ0

00000000

1 Level 0 00000100

2 IRQ1

00001000

3 Level 1 00001100

4 IRQ2

00010000

5 Level 2 00010100

6 IRQ3

00011000

7 Level 3 00011100

8 IRQ4

00100000

9 Level 4 00100100

10 IRQ5

00101000

11 Level 5 00101100

12 IRQ6

00110000

13 Level 6 00110100

14 IRQ7

00111000

15 Lowest Level 7 00111100

16-31 Reserved —

Loading...

Loading...