The PowerPC Core

6-26 MPC823e REFERENCE MANUAL MOTOROLA

CORE

6

To execute multiple (lmw, stmw) instructions, string instructions, and unaligned accesses,

the load/store unit contains an address incrementor that generates the needed addresses.

This allows the unit to execute the unaligned accesses without stalling the master instruction

pipeline.

6.6.1 Issuing Load/Store Instructions

When load or store instructions are encountered, the load/store unit checks the scoreboard

to determine if all of the operands are available. These operands include:

• Address register operands

• Source data register operands (for store instructions)

• Destination data register operands (for load instructions)

• Destination address register operands (for load/store with update instructions)

If all operands are available, the load/store unit takes the instruction and enables the

sequencer to issue a new instruction. Then, using a dedicated interface, the load/store unit

notifies the integer unit of the need to calculate the effective address. All load/store

instructions are executed and terminated in order.

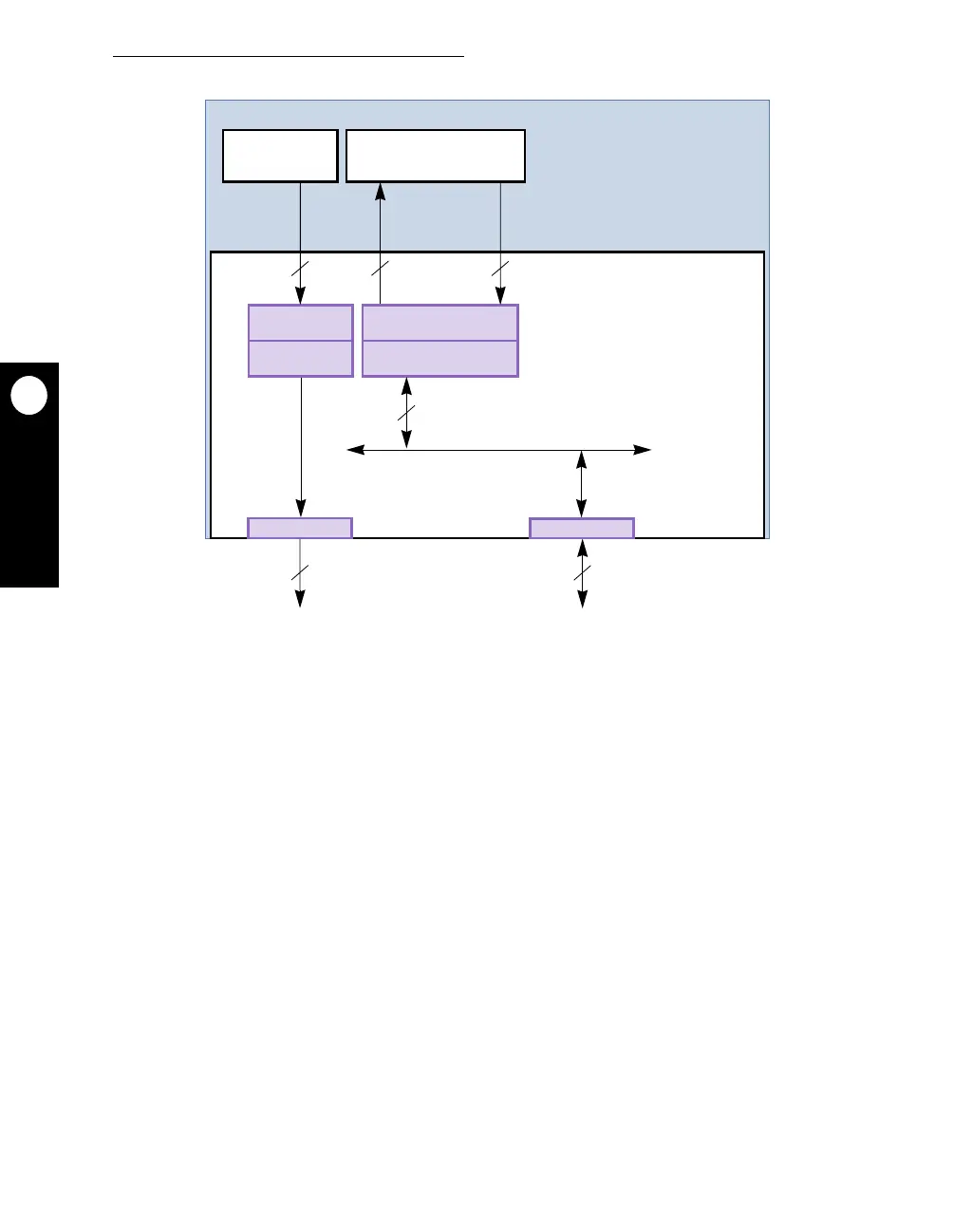

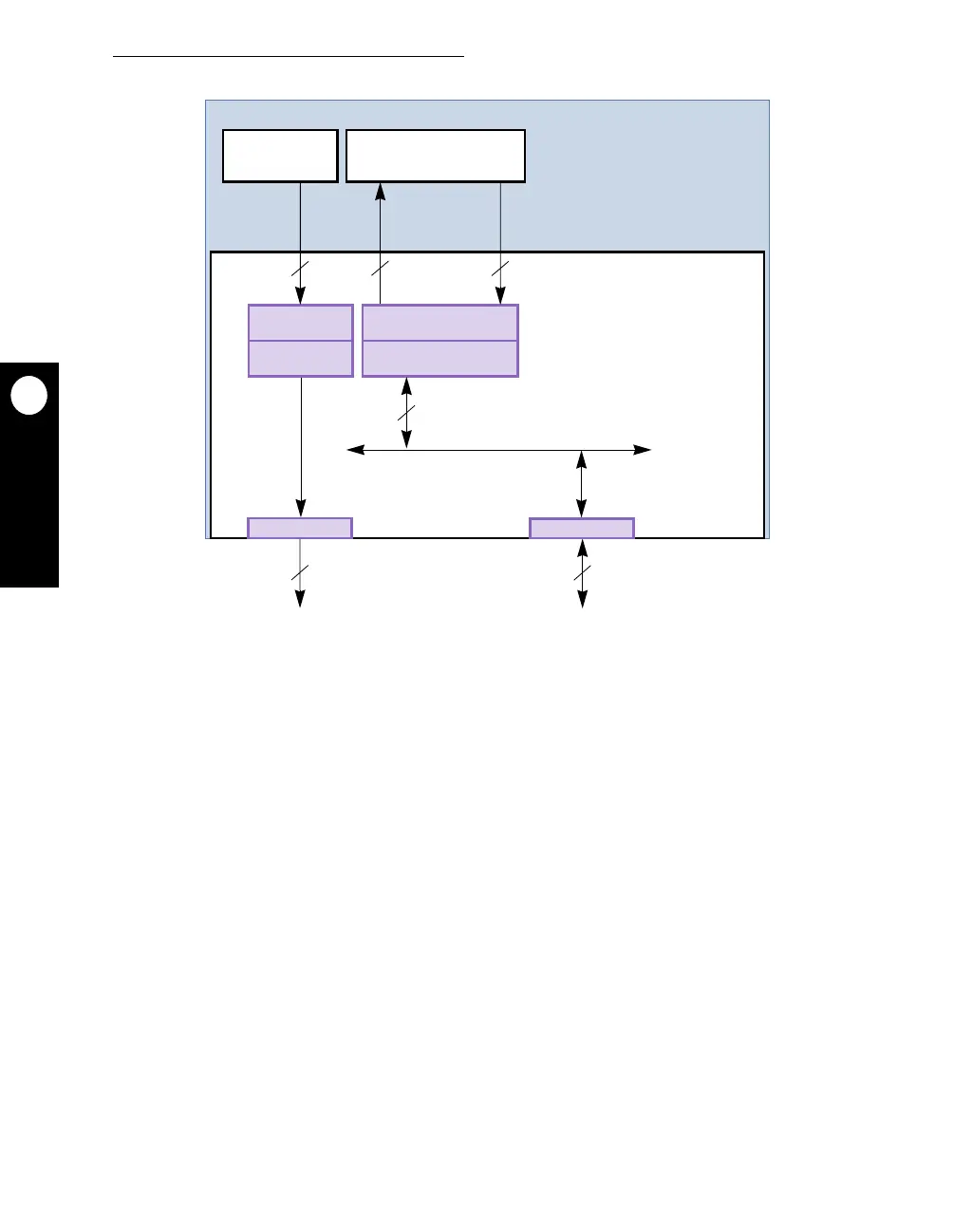

Figure 6-6. Load/Store Unit Functional Block Diagram

FIXED-POINT

QUEUE

ADDRESS FIXED-POINT

STORE DATA

LOAD / STORE UNIT

FIXED-POINT

LOAD DATA

D-CACHE / D-MMU

CORE

32

FIXED-POINT

REGISTERS FILE

FIXED-POINT

UNIT

32 32

32

ADDRESS

QUEUE

INCREMENT

AND

DATA

32

32

INTERFACE

Loading...

Loading...