System Interface Unit

MOTOROLA MPC823e REFERENCE MANUAL 12-29

SYSTEM INTERFACE UNIT

12

12.11 MULTIPLEXING THE SYSTEM INTERFACE UNIT PINS

Due to the limited number of pins available in the MPC823e package, some of the

functionalities share pins. The actual MPC823e pinout is illustrated in

Section 2 External Signals. The following table shows how the functionality is controlled

on each pin.

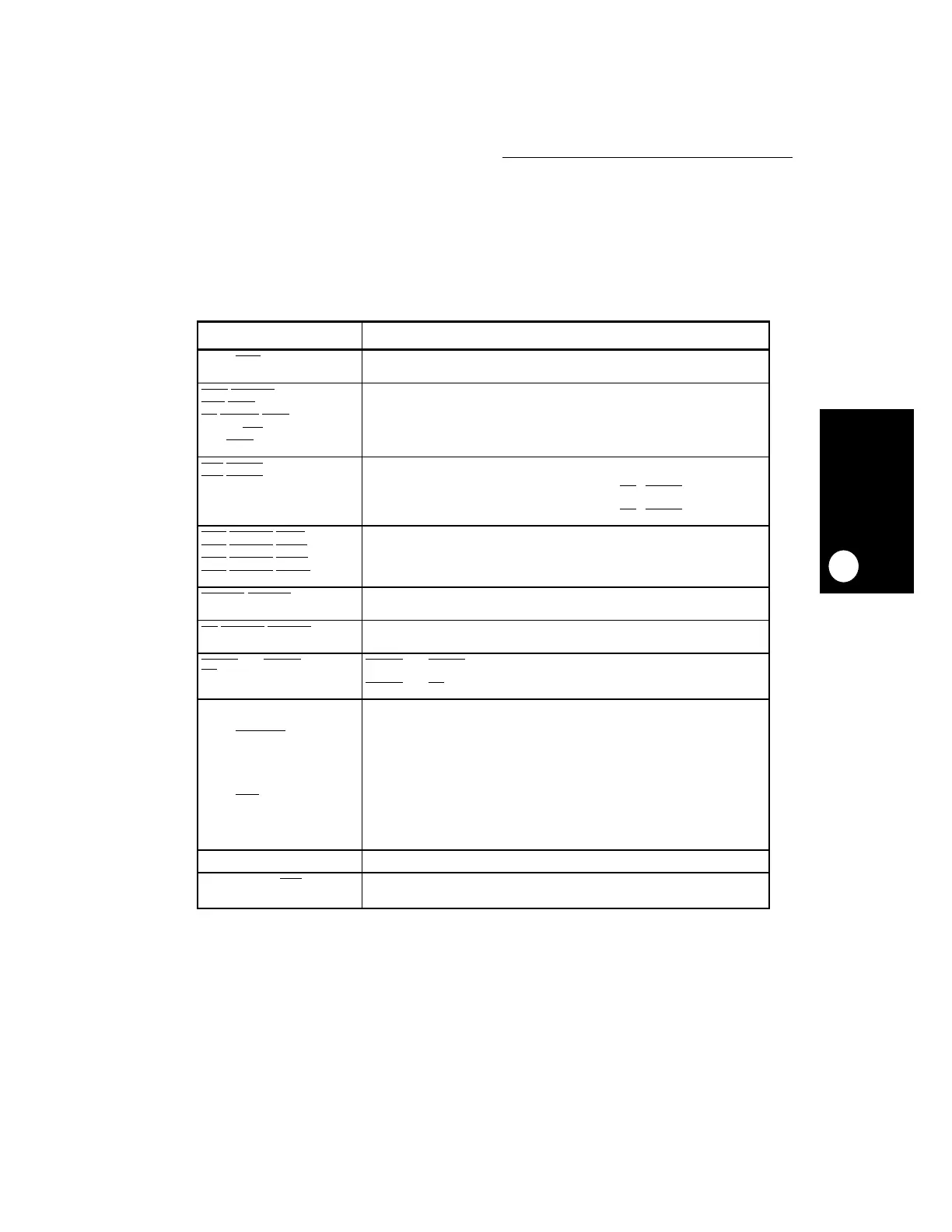

Table 12-2. Multiplexing Control

PIN NAME PIN CONFIGURATION CONTROL

TSIZ0/REG

Dynamically active depending if the transaction addresses a slave controlled by

the PCMCIA interface.

BDIP

/GPL_B5

RSV/IRQ2

KR/RETRY/IRQ4/SPKROUT

DP[0:3]/IRQ

[3:6]

FRZ/IRQ6

Programmed in the SIUMCR.

CS6

/CE1_B

CS7/CE2_B

Address matching and bank valid bits.

When there is a transfer such that there is a match in either memory controller

bank 6 or any PCMCIA bank mapped to slot B, the CS6/CE1_B will be asserted.

When there is a transfer such that there is a match in either memory controller

bank 7 or any PCMCIA bank mapped to slot B, the CS7/CE2_B will be asserted.

WE0/BS_AB0/IORD

WE1/BS_AB1/IOWR

WE2/BS_AB2/PCOE

WE3/BS_AB3/PCWE

Dynamically active depending on the machine (GPCM, UPMB, or PCMCIA

interface) assigned to control the required slave.

GPL_A0

/GPL_B0 Dynamically active depending on the machine (UPMA or UPMB) assigned to

control the required slave.

OE

/GPL_A1/GPL_B1 Dynamically active depending on the machine (GPCM, UPMA, or UPMB)

assigned to control the required slave.

GPL_A

[2:3]/GPL_B[2:3]/

CS

[2:3]

GPL_A

[2:3]/GPL_B[2:3]: Dynamically active depending on the machine

(UPMA or UPMB) assigned to control the required slave.

GPL_A[2:3]/CS[2:3]: Programmed in the SIUMCR.

ALE_B/DSCK/AT1

IP_B[0:1]/IWP[0:1]/VFLS[0:1]

IP_B2/IOIS16_B

/AT2

IP_B3/IWP2/VF2

IP_B4/LWP0/VF0

IP_B5/LWP1/VF1

IP_B6/DSDI/AT0

IP_B7/PTR

/AT3

TDI/DSDI

TCK/DSCK

TDO/DSDO

Programmed in the SIUMCR and hard reset configuration.

UPWAITA/GPL_A4/AS Programmed in the SIUMCR and MAMR of the memory controller.

OP2/MODCK2/STS

OP3/MODCK2/DSDO

At power-on reset, this functions as MODCK[1:2]

Otherwise, programmed in the SIUMCR and hard reset configuration.

Loading...

Loading...