System Interface Unit

MOTOROLA

MPC823e REFERENCE MANUAL

12-11

SYSTEM INTERFACE UNIT

12

12.4 THE BUS MONITOR

The bus monitor ensures that each bus cycle is terminated within a reasonable period of

time. The MPC823e system interface unit provides a bus monitor option that monitors

internally generated external bus accesses on the external bus. At the start of the transfer

start (TS

) signal, the monitor begins counting and stops when the transfer acknowledge (TA)

or transfer error (TEA

) signal is asserted. Within the bus cycle, the burst cycle performs

three functions—stops the previous count, resets, and restarts a new count until the next

transfer acknowledge. The last transfer acknowledge of the burst cycle only stops the

counter. When a RETRY

signal is asserted, it has the same effect as the TA or TEA signal.

If the monitor times out, a TEA

signal is internally asserted by the bus monitor to terminate

the cycle. The programmability of the timeout allows for a variation in system peripheral

response time. The timing mechanism is clocked by the system clock divided by eight. The

maximum value can be 2,040 system clocks. The bus monitor will always be active when

the FRZ signal is asserted or when a debug mode request is pending, regardless of the state

of the BMT bit.

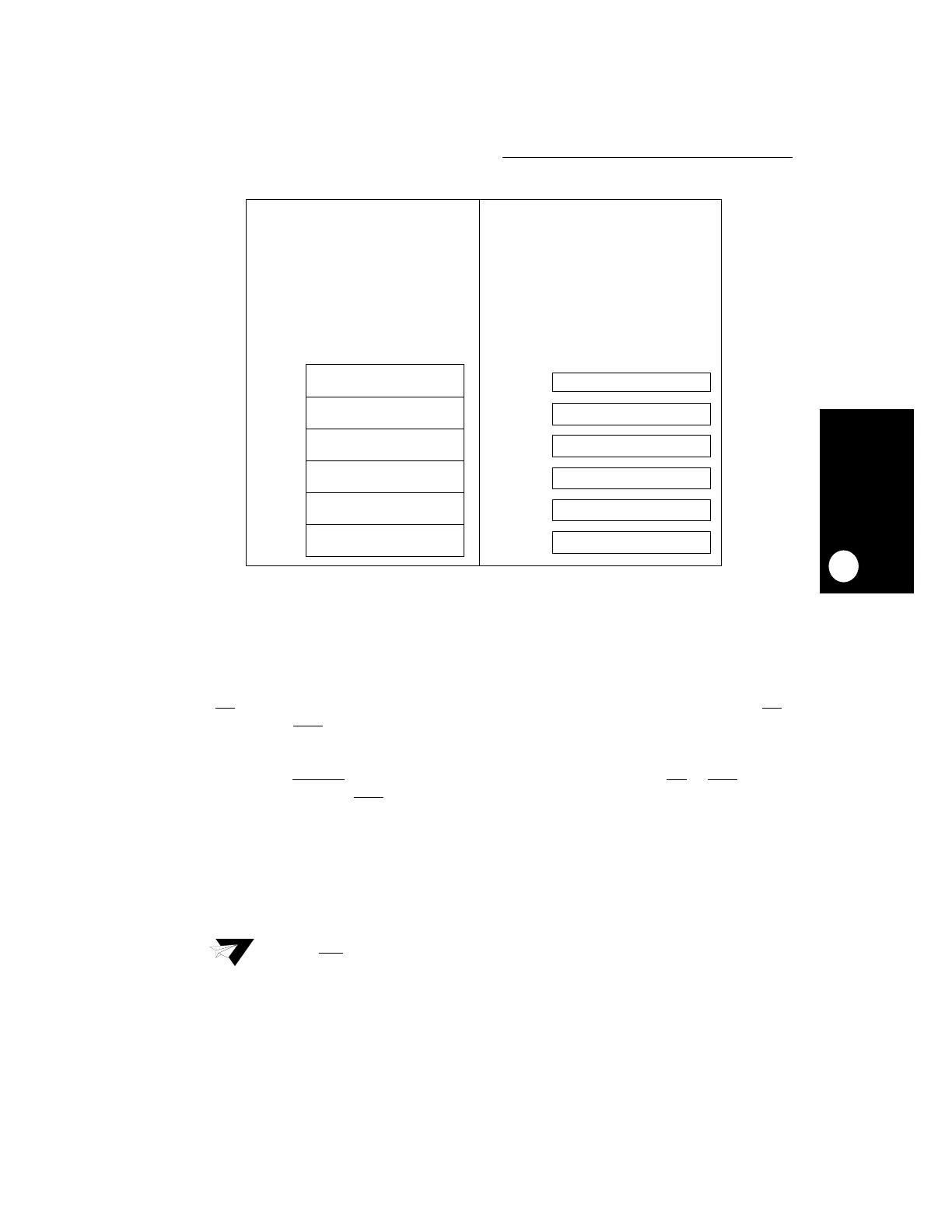

Figure 12-3. Interrupt Table Handling Example

Note:

If the bus monitor is disabled, the transfer error conditions will not assert the

TEA

pin.

BASE b Routine1

b Routine2

b Routine3

b Routine4

•

•

BASE + n

BASE + 4

BASE + 8

BASE + C

BASE +10

BASE

1st Instruction of Routine1

1st Instruction of Routine2

1st Instruction of Routine3

1st Instruction of Routine4

•

•

BASE + n

BASE + 400

BASE + 800

BASE + C00

BASE +1000

•

•

•

•

•

•

INTR: • • •

Save state

R3 <- @ SIVEC

R4 <-- Base of branch table

• • •

lbz

add

mtspr

bctr

RX, R3 (0)

# load as byte

RX, RX, R4

CTR, RX

INTR: • • •

Save state

R3 <- @ SIVEC

R4 <-- Base of branch table

• • •

lhz

add

mtspr

bctr

RX, R3 (0)

# load as byte

RX, RX, R4

CTR, RX

Loading...

Loading...