The PowerPC Core

6-8

MPC823e REFERENCE MANUAL

MOTOROLA

CORE

6

6.3.4 Implementing the Precise Exception Model

To achieve maximum performance, many pieces of the instruction stream are concurrently

processed by the core independent of the sequence specified by the executing program.

Instructions execute in parallel and are completely random. The hardware ensures that this

out-of-order operation never has an effect different than that specified by the program. This

requirement is most difficult to assure when an interrupt occurs after instructions that

logically follow the faulting instruction or have already completed. At the time of an interrupt,

the machine state becomes visible to other processes and, therefore, must be in the

appropriate architecturally specified condition. The core takes care of this in the hardware

by automatically backing up the machine to the instruction which caused the interrupt and

is, therefore, said to implement a precise exception model. This is, of course, assuming that

the instruction causing the exception has not begun when the interrupt occurs.

To recover from an interrupt, a history buffer is used. This buffer is a FIFO queue that

records the relevant machine state at the time of each instruction issue. Instructions are

placed on the tail of the queue when they are issued and percolated to the head of the queue

while they are in execution. Instructions remain in the queue until they complete execution

and all preceding instructions have been completed to a point where no exception can be

generated (in the core, such a condition is fulfilled by waiting for full completion).

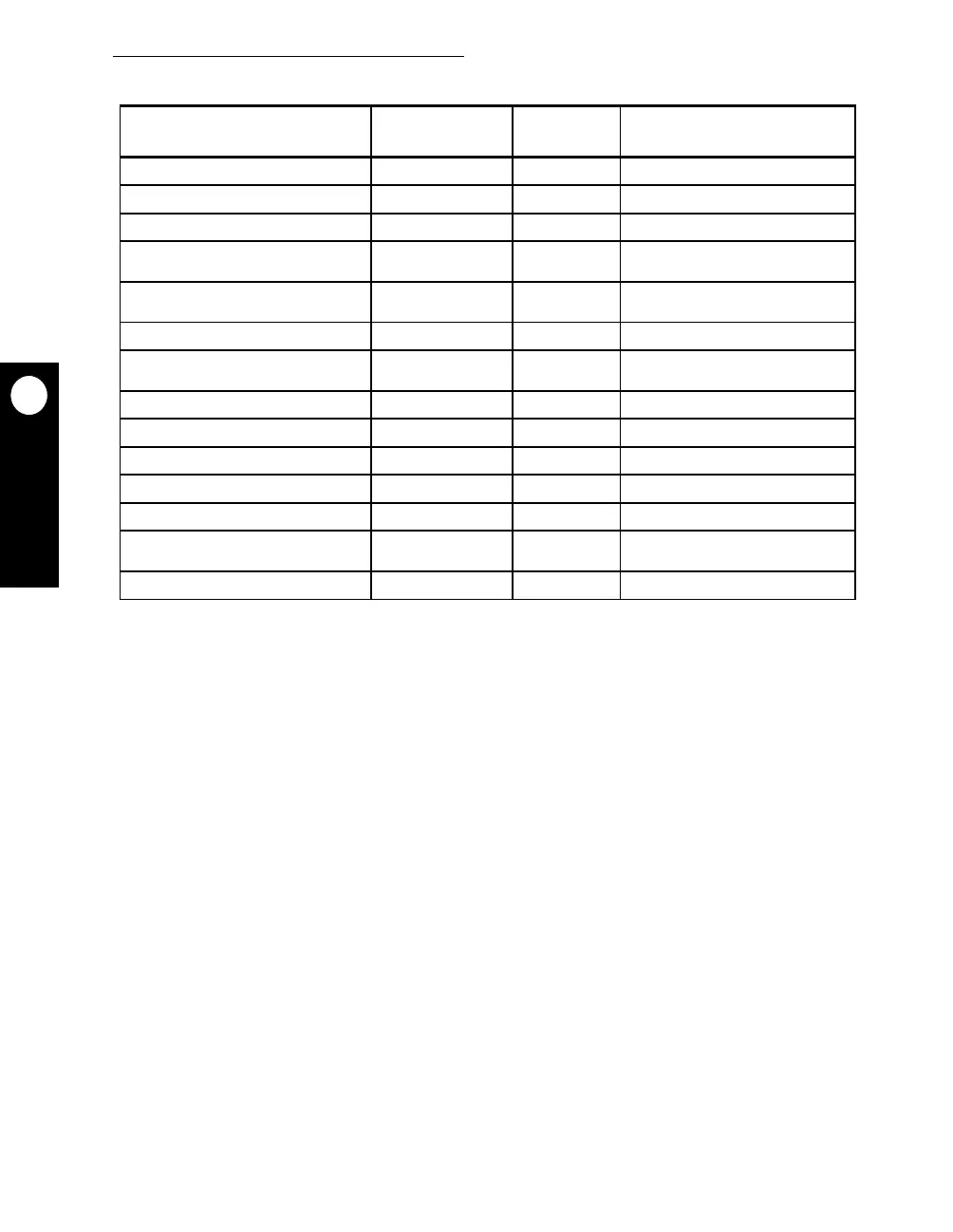

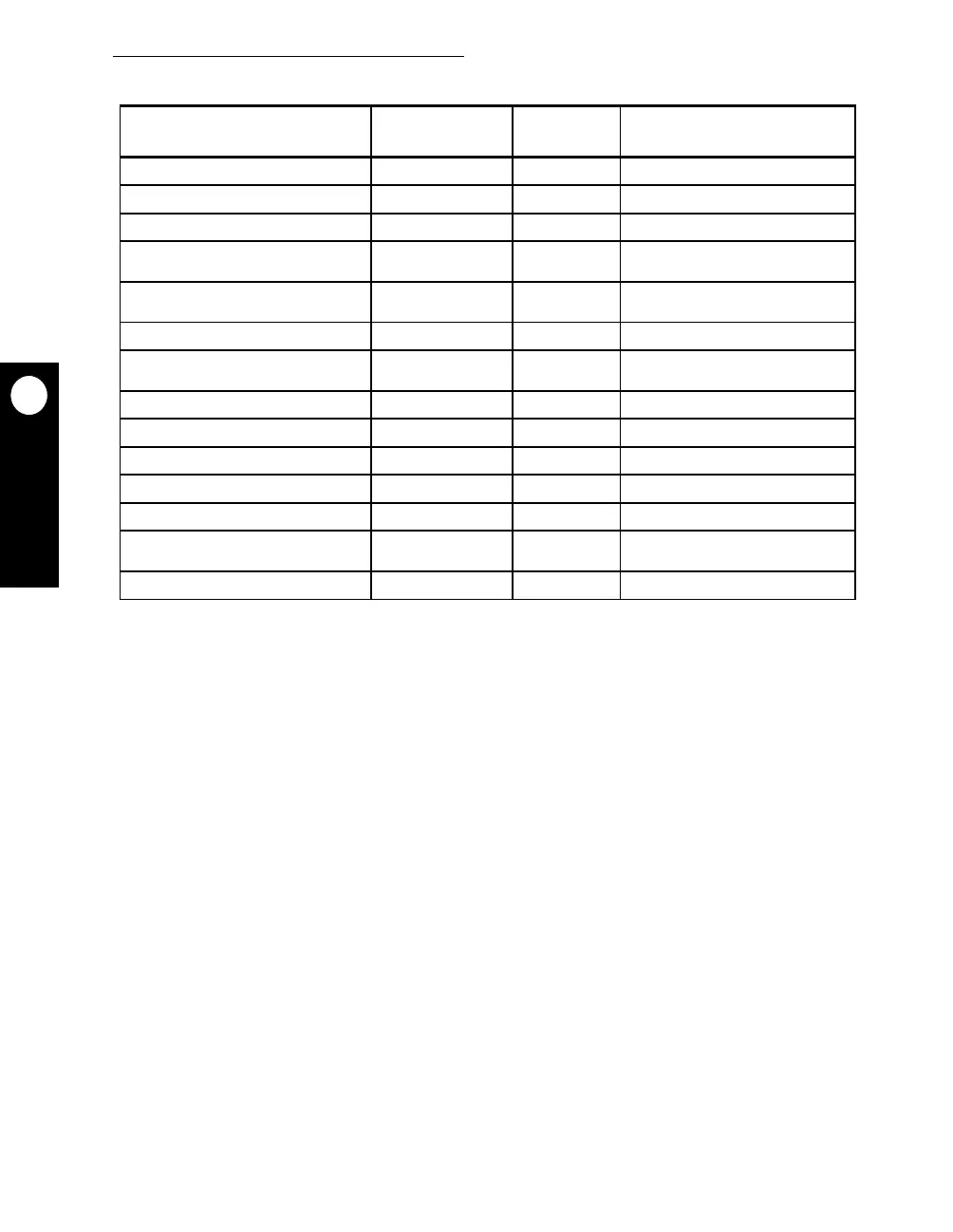

Table 6-2. Before and After Interrupts

INTERRUPT TYPE INSTRUCTION

TYPE

BEFORE /

AFTER

CONTENTS OF SRR0

Hard Reset Any NA Undefined

System Reset Any Before Next Instruction to Execute

Machine Check Interrupt Any Before Faulting Instruction

Implementation Specific Instruction /

Data TLB Miss / Error Interrupts

Any Before Faulting Fetch or Load/Store

Other Asynchronous Interrupts

(Noninstruction Related Interrupts)

Any Before Next Instruction to Execute

Alignment Interrupt Load / Store Before Faulting Instruction

Privileged Instruction Any Privileged

Instruction

Before Faulting Instruction

Trap tw, twi Before Faulting Instruction

System Call Interrupt sc After Next Instruction to Execute

Trace Any After Next Instruction to Execute

Debug I- Breakpoint Any Before Faulting Instruction

Debug L- Breakpoint Load / Store After Faulting Instruction + 4

Implementation Dependent Software

Emulation Interrupt

NA Before Faulting Instruction

Floating-Point Unavailable Floating-Point Before Faulting Instruction

Loading...

Loading...