MOTOROLA

MPC823e REFERENCE MANUAL

8-1

INSTRUCTION EXECUTION

8

TIMING

SECTION 8

INSTRUCTION EXECUTION TIMING

This section describes the timing of the instruction cycles in terms of clock cycles, including

serialization, latency, and blockage.

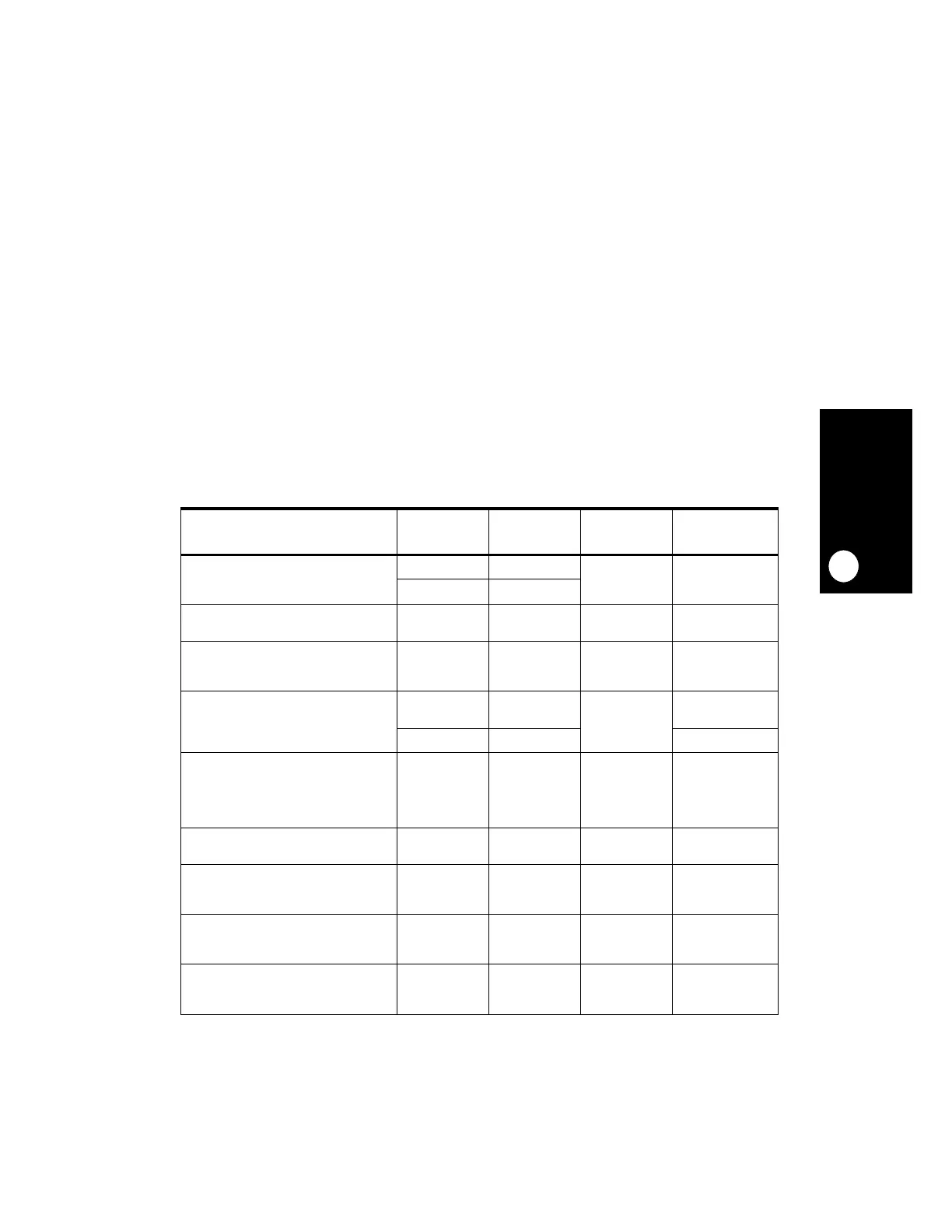

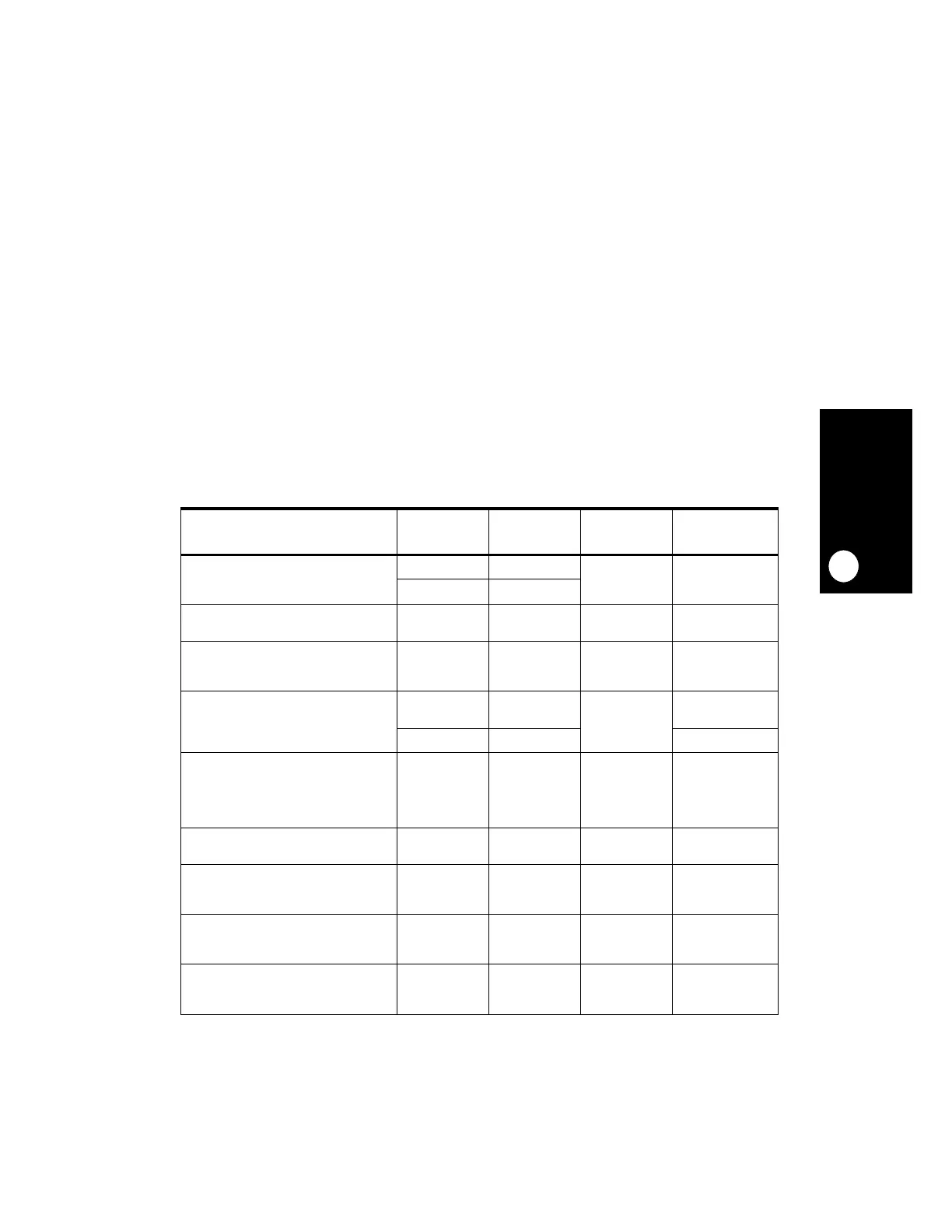

8.1 INSTRUCTION TIMING LIST

The following table lists the instruction execution timing in terms of latency and blockage of

the appropriate execution unit. A serializing instruction has the effect of blocking all

execution units.

Table 8-1. Instruction Execution Timing

INSTRUCTIONS LATENCY BLOCKAGE EXECUTION

UNIT

SERIALIZING

INSTRUCTION

Branch Instructions:

b, ba, bl, bla, bc, bca, bcl, bcla, bclr,

bclrl, bcctr, bcctl

Taken 2 2 Branch Unit No

Not Taken 1 1

System Call:

sc, rfi

Serialize + 2 Serialize + 2 — Yes

CR Logical:

crand, crxor, cror, crnand, crnor,

crandc, creqv, crorc, mcrf

1 1 CR Unit No

Fixed-Point Trap Instructions:

twi, tw

Taken

Serialize + 3

Serialize + 3 ALU / BFU After

Not Taken 1 1 No

Move to Special Registers:

mtspr, mtcrf, mtmsr, mcrxr

Except mtspr to LR and CTR and

External to the Core Registers

Serialize + 1 Serialize + 1 All Yes

Move to LR, CTR:

mtspr

1 1 Branch Unit No

Move to External to the Core

Special Registers:

mtspr, mttb, mttbu

Serialize + 1

8

Serialize + 1 LDST Yes

Move from External to the Core

Special Registers:

mfspr, mftb, mftbu

Load Latency 1 LDST No

Move from Special Registers

Located Internal to the Core:

mfspr

1

11—

See List

2

Loading...

Loading...