Instruction Execution Timing

8-4

MPC823e REFERENCE MANUAL

MOTOROLA

INSTRUCTION EXECUTION

8

TIMING

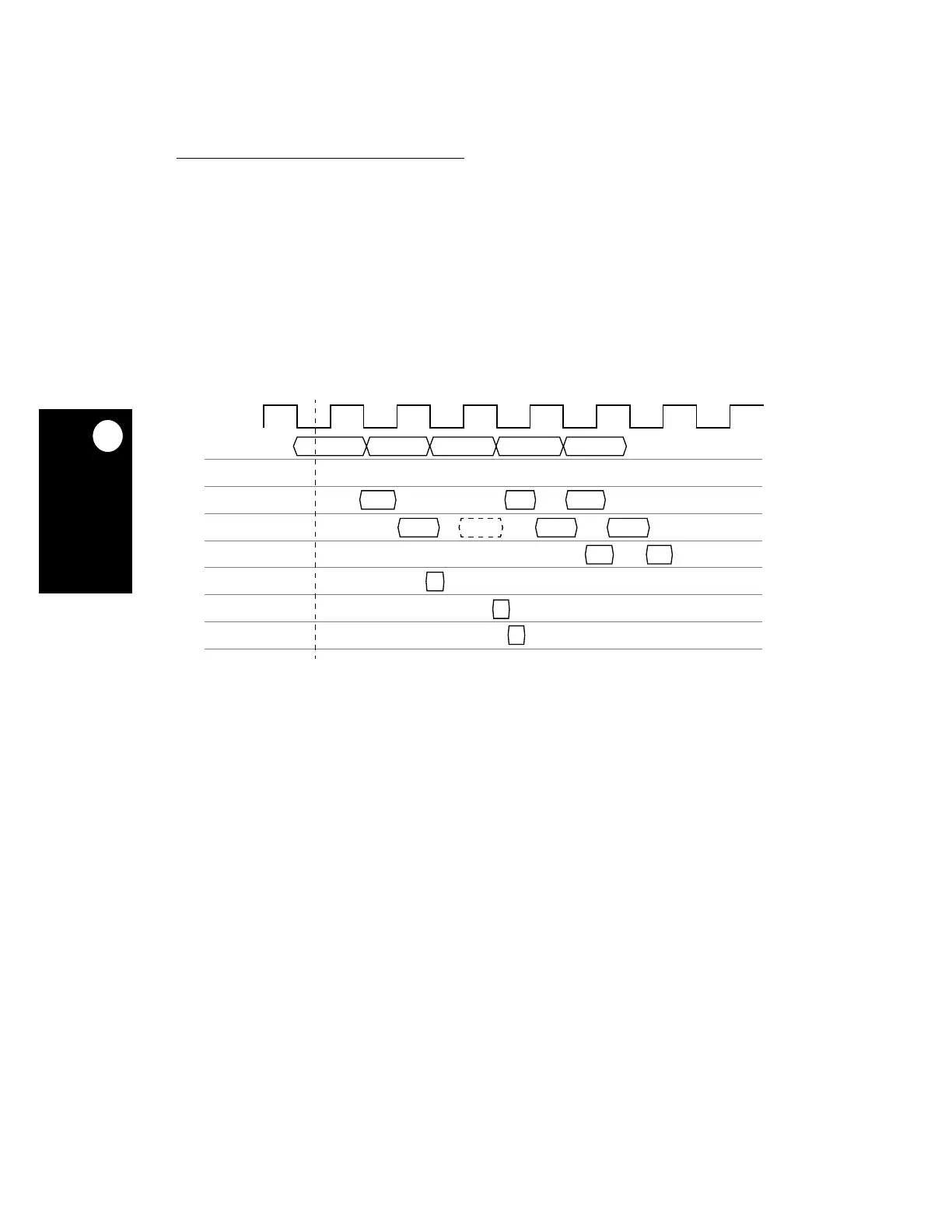

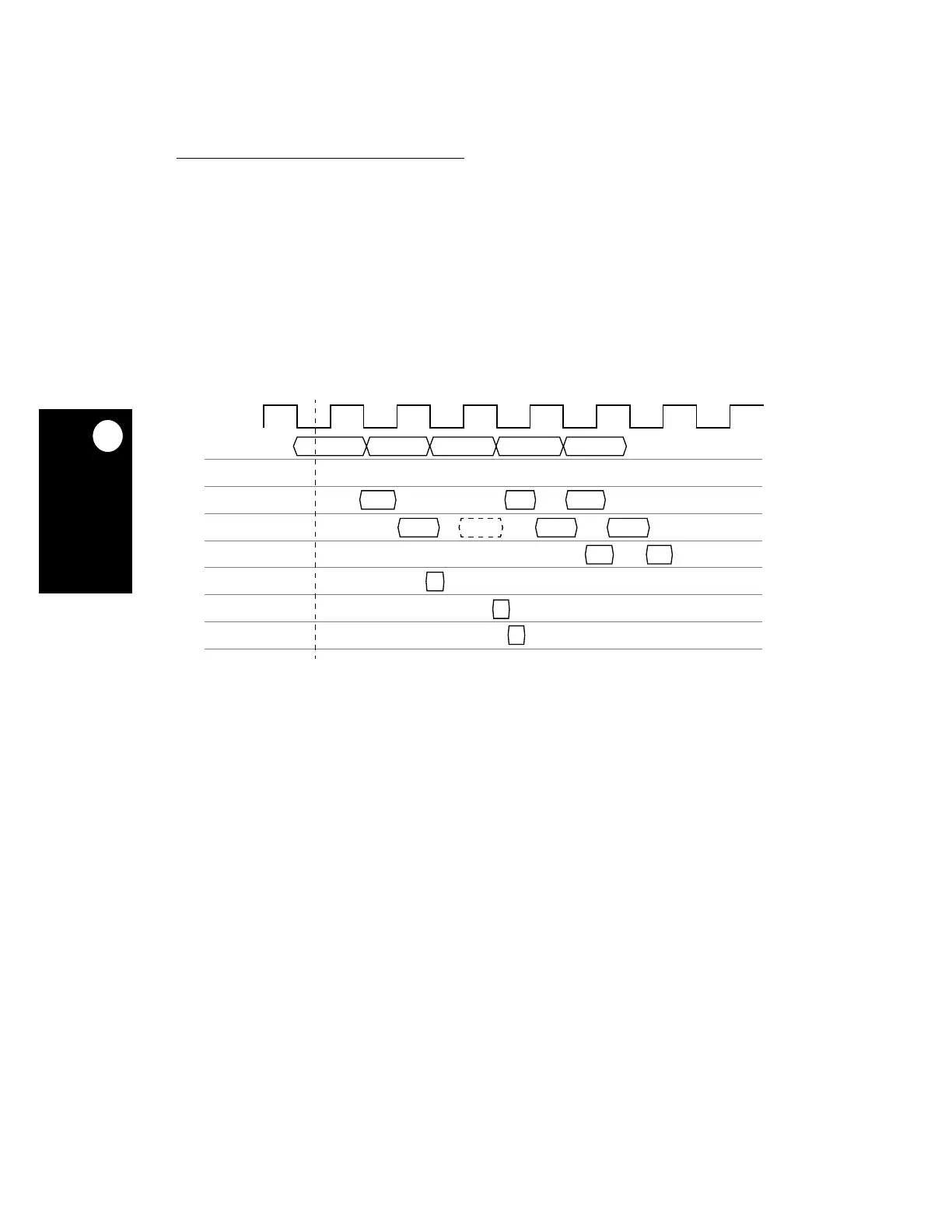

8.2 INSTRUCTION EXECUTION TIMING EXAMPLES

All examples assume an instruction cache hit.

8.2.1 Data Cache Load

lwz

r12,64 (SP)

sub

r3,r12,3

addic

r4,r14,1

mulli

r5,r3,3

addi

r4,3(r0)

This is an example from a data cache with zero wait states. The

sub

instruction is dependent

on the value loaded by the load to r12. This causes a bubble to occur in the instruction

stream as shown in the execute line. Refer to

Section 8.2.2.2 Private Writeback Bus Load

for instances in which no such dependency exists.

Figure 8-1. Example of a Data Cache Load

LWZ SUB MULLI ADDIADDIC

FETCH

DECODE

READ + EXECUTE

WRITEBACK

L ADDRESS DRIVE

L DATA

LOAD WRITE BACK

LWZ SUB

BUBBLE

ADD

ADDIC

LWZ SUB

SUB

ADDIC

LD

LD

LD

Loading...

Loading...