Do you have a question about the Honeywell HPM and is the answer not in the manual?

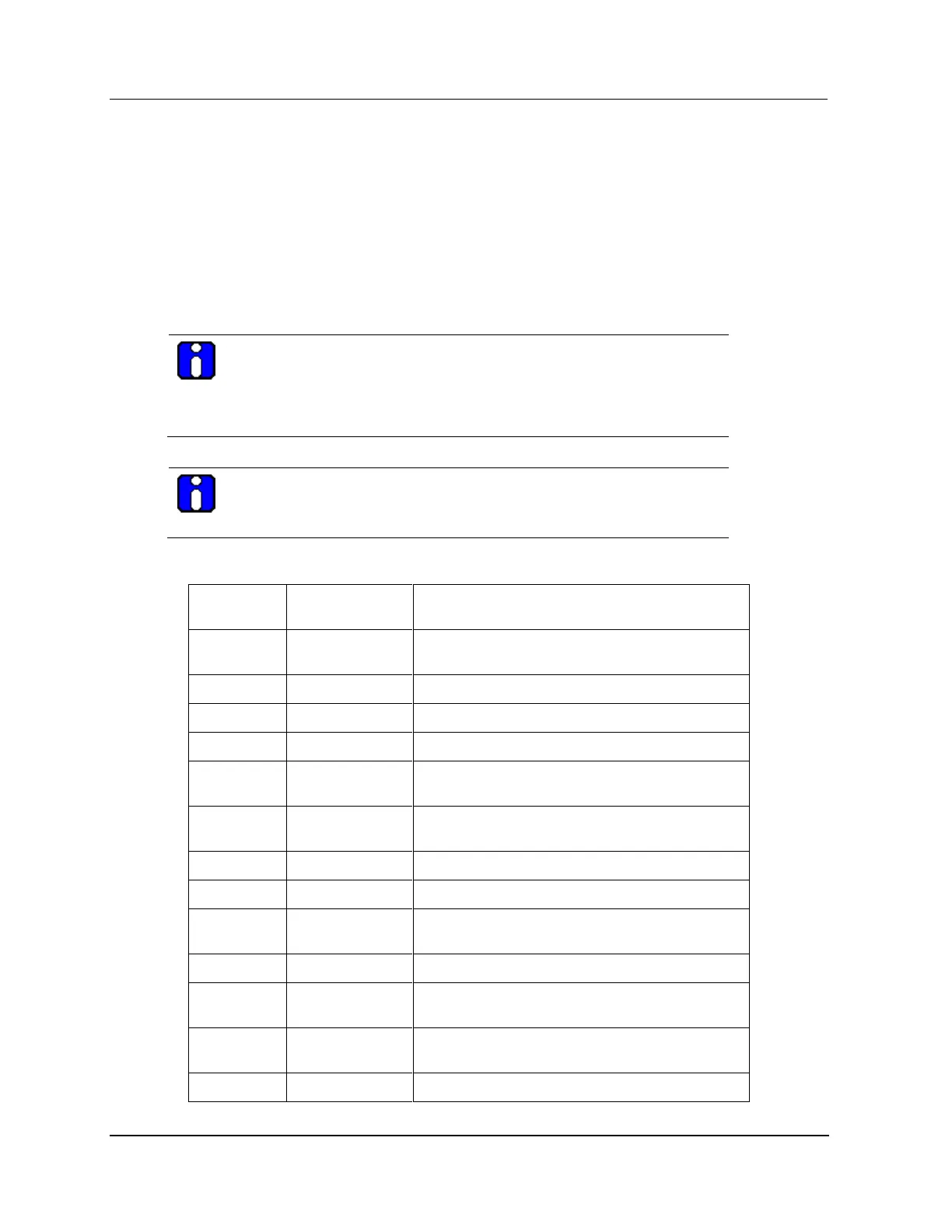

| Brand | Honeywell |

|---|---|

| Model | HPM |

| Category | Network Hardware |

| Language | English |

Provides an overview of the HPM subsystem, including major assemblies and card file types.

Discusses differences between HPMM and IOP card files, including models and conversion kits.

Details HPMM card file configurations, functionality, card types, indicators, and diagnostic displays.

Describes EHPM card file configurations, functionality, card types, indicators, and diagnostic displays.

Provides procedures for servicing failed EHPM cards flashed with Experion-integrated firmware.

Describes I/O Link Extender features, guidelines, front panel indicators, and status indicators.

Discusses Power System features, types, 48-volt battery backup time, and CMOS backup time.

Details 24 Vdc fuse protection for card files, including fuse removal and insertion.

Covers 5 Vdc fuse protection for High-Performance I/O Link cards and HPMM components.

Covers I/O Link interface cabling, including cable length, redundant cables, and shield grounding.

Explains the Universal Control Network (UCN) cable system, including components and cable taps.

Covers the Enhanced Universal Control Network (EUCN) cable system, including FTE cables and fault diagnosis.

Defines Hard failures and Soft failures and their impact on HPM and IOP components.

Provides a procedure for diagnosing failures in redundant Analog Output IOPs.

Provides ESD prevention rules and guidelines for handling HPMM and IOP cards.

Details removal and replacement procedures for HPMM and IOP cards, including interface modules.

Covers common calibration procedures for LLAI, AO, and HLAI subsystems, including IOP/FTA substitution.

Details LLAI IOP calibration, including ranges, slot effects, range selection, and RTD/TC calibration.

Provides calibration procedures for nonredundant HLAI FTAs, including connection points and terminals.

Details simultaneous IOP calibration for redundant HLAI IOPs, including connections.

Provides calibration procedures for nonredundant AO IOPs, including isolation and calibration targets.

Details simultaneous IOP calibration for redundant AO IOPs, requiring specific FTA connections.

Discusses HPMM redundancy and how to confirm swap positions using display commands.

Explains IOP redundancy terminology and provides a test procedure for redundant IOP configurations.

Details redundancy for 8-channel Analog Output IOPs, including hardware identification and test procedures.

Covers redundant power cables for card files and distribution assemblies, including testing procedures.

Discusses Power System redundancy and the test procedure for power capability.