Appendix F ___________________________________________________ RCP902 WSR98D Panel

VAISALA______________________________________________________________________ 471

F.9 Software Control/Status

Many of the signals on the WSR98D panel are driven real-time by the

RVP900 IFDR controlled by the RVP900 process or on a sampled basis by

either the RVP900 or RCP8 processes. If controlled by the RCP8 process,

they are mapped to logical variables in the softplane.conf file.

F.9.1 Logical Variables

For logic mappings to be valid, the settings in Table 33 must be defined in

the softplane.conf file.

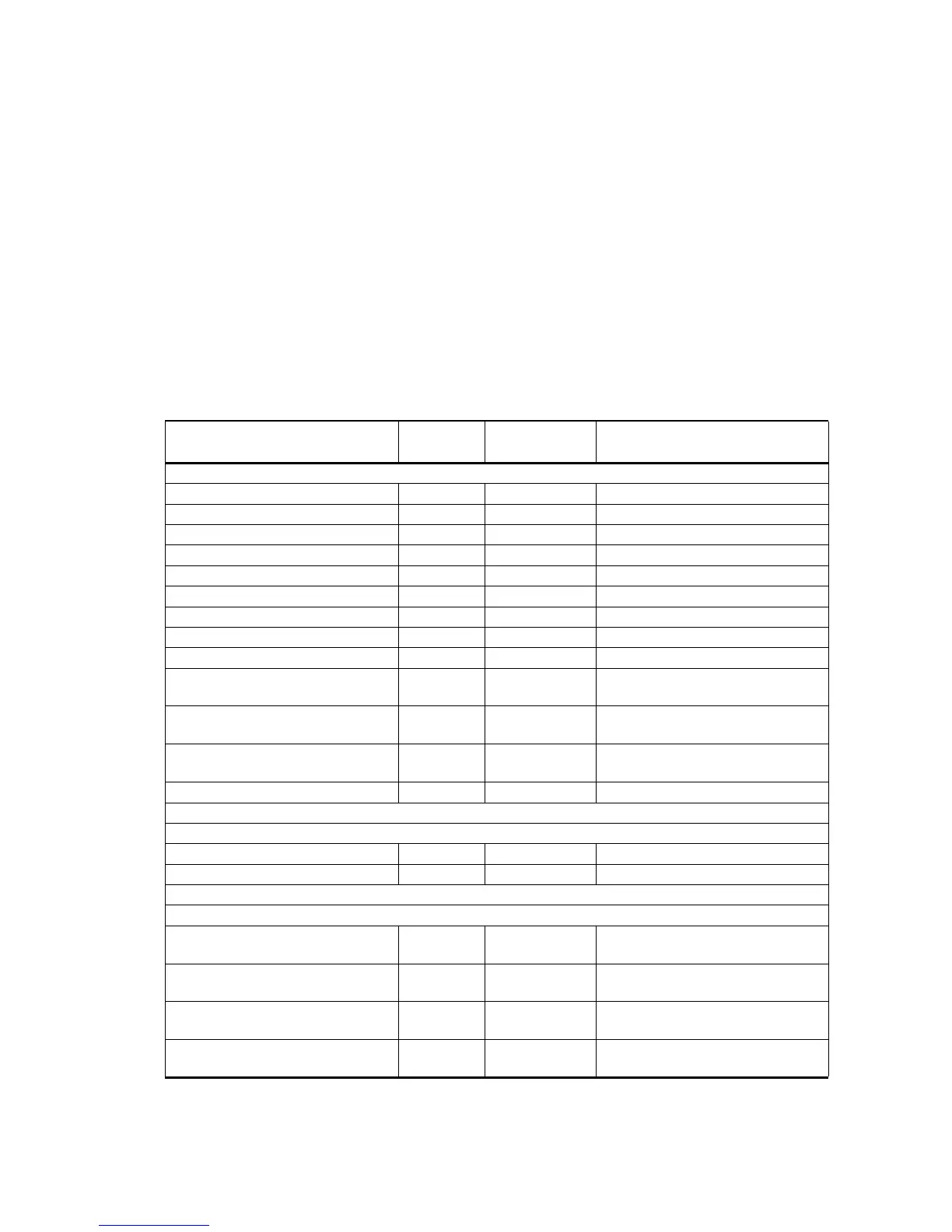

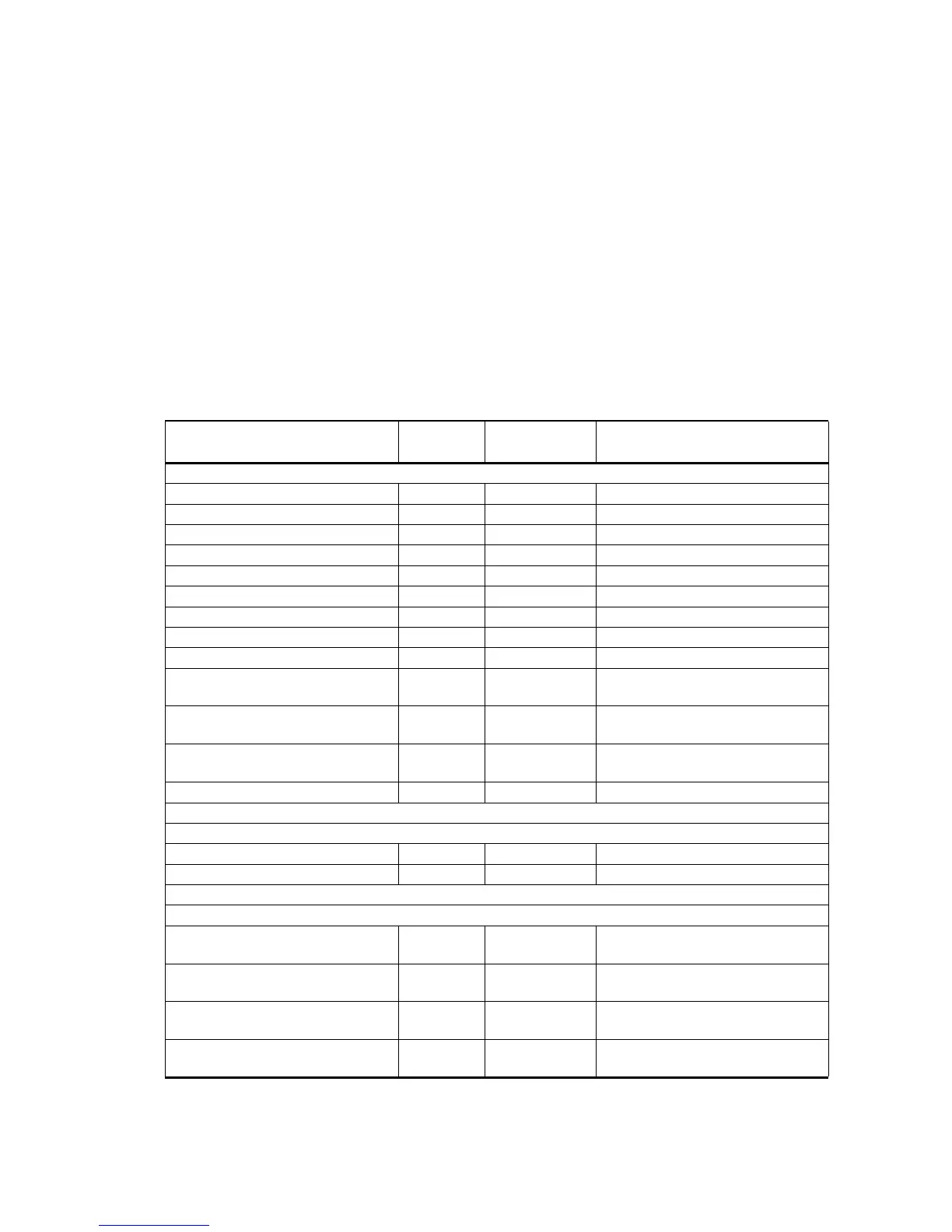

Table 33 Software Control/Status Variable

Signal Name Controlling

Process

Programmable

Logic Variable

Conditions

J3

NC

RF_PULSE_START_TRG_P/N RVP trigger 2

RF_DRIVE_TRG_P/N RVP trigger 6

FILAMENT_RESET_TRG_P/N RVP trigger 5

POST_CHARGE_TRG_P/N RVP trigger 7

MOD_CHARGE_TRG_P/N RVP trigger 4

MOD_DISCHARGE_TRG_P/N RVP trigger 3

SHORT_BEAM_PULSE_SEL_P/N RCP cAux[27]

SHORT_RF_PULSE_SEL_P/N RCP cAux[28]

PULSE_RATE_IN_P/N0 RVP Latched in on falling edge of

trigger 10

PULSE_RATE_IN_P/N1 RVP Latched in on falling edge of

trigger 10

PULSE_RATE_IN_P/N2 RVP Latched in on falling edge of

trigger 10

TRIGGER_CHARGE_TRG_P/N RCP trigger 8

J4

RCVR_PROTECT_RSP_P RCP sAux[30]

RCVR_PROTECT_CMD_P RVP / RCP trigger 9 cAux[24] forces RX Protect Mode

J7

PHASEBIT_P/N7 RVP Latched in on rising edge of

trigger 10

PHASEBIT_P/N6 RVP Latched in on rising edge of

trigger 10

PHASEBIT_P/N5 RVP Latched in on rising edge of

trigger 10

PHASEBIT_P/N4 RVP Latched in on rising edge of

trigger 10

Loading...

Loading...