Chapter 3 _______________________________________________________ Hardware Installation

VAISALA_______________________________________________________________________ 67

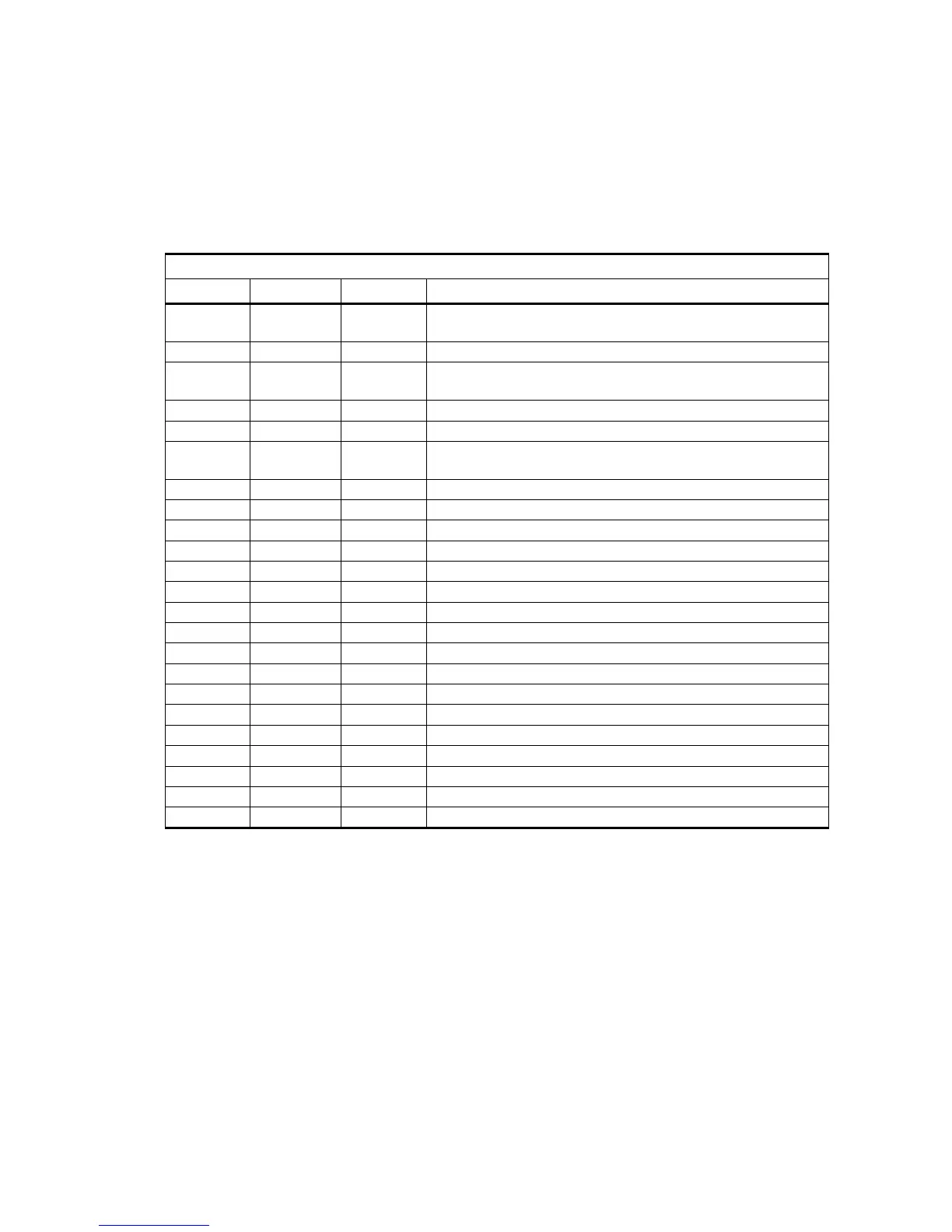

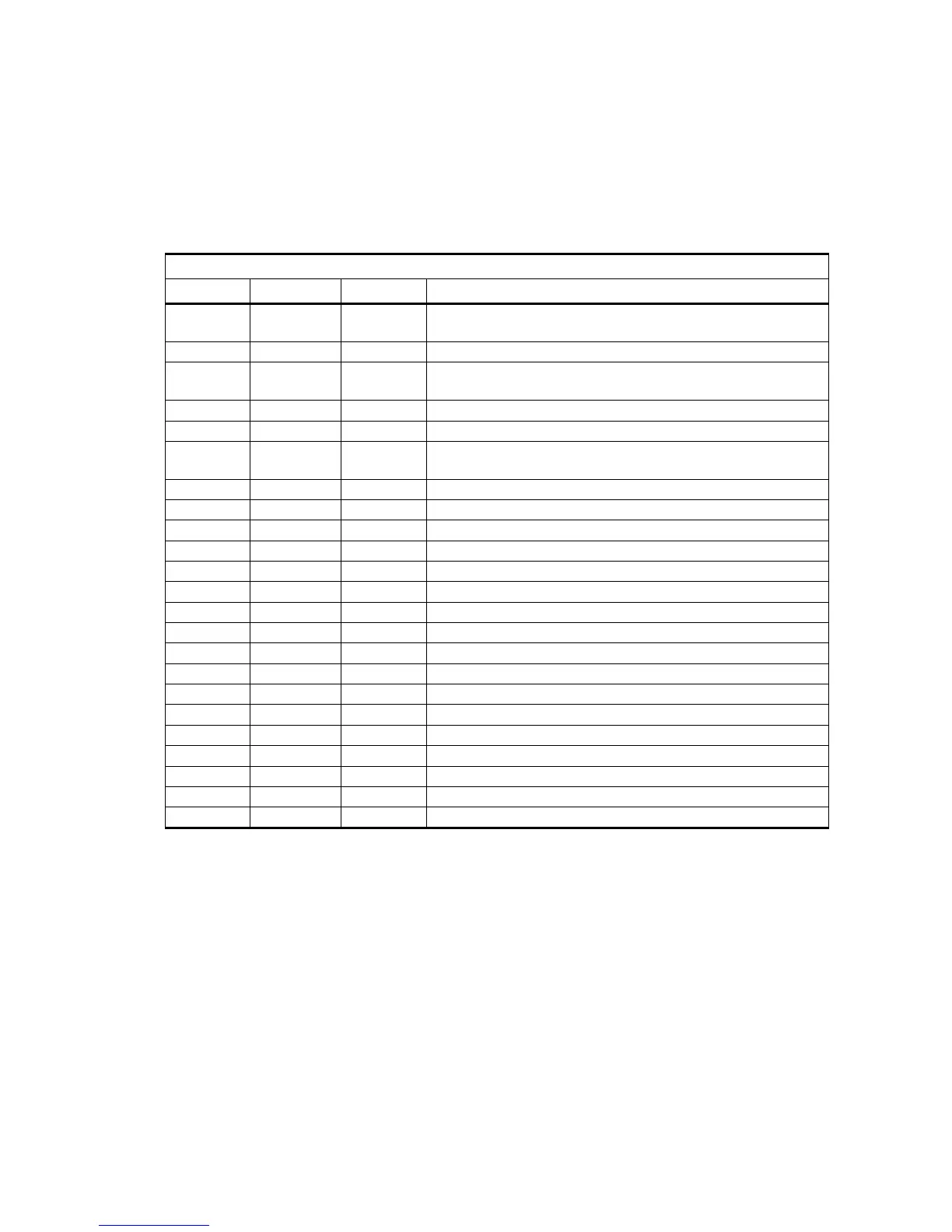

3.2.4 IFDR I/O Summary

The connectors on the IFDR are labelled and described in Table 3. IFDR

Connectors on page 65.

3.2.5 IFDR Status Indicators

The IFDR is packaged in a tight metal enclosure for maximum noise

immunity. Two LEDs provide status information for the IFDR and status

of the communication links to the RVP902. These LEDs have the same

interpretation as the RVP7 and RVP8 LED indicators.

Table 3 IFDR Connectors

RVP901 Connector Panel Summary

J-ID Label Type Description

J1 DC IN MINIFIT

2X2

Power Supply Input

J2 ETHERNET RJ-45 Ethernet connection to host computer

J3 MISC I/O-B 51-Pin

Micro-D

Each Micro

-D has an identical pinout

J4 UP LINK RJ-45 Gigabit serial Link

J5 DN LINK RJ-45 Same as J4

J6

MISC I/O

-A

51-Pin

Micro-D

Same as J3

J7 CLK IN SMA Reference Clock Input

J8 TRIG-B SMA General purpose trigger I/O

J9 CLK OUT SMA Reference Clock Output

J10 DDS SMA Direct Digital Synthesizer Output

J11 TxDAC-B SMA Direct Transmit IF output

J12 TxDAC-A SMA Same as J11

J13A ADC-A SMA Direct IF Input. IF-1 for single channel or primary polarization

J13B ADC-B SMA Direct IF Input. IF-2 for secondary polarization

J13C ADC-C SMA Direct IF Input

J13D ADC-D SMA Direct IF Input

J13E ADC-E SMA Direct IF Input. Burst Sample Input

J14 VIDEO OUT SMA Video DAC output, synthesizes simple video waveforms

J15 TRIG-A SMA General purpose trigger I/O or DAFC interface

SW1 Switch Tactile, momentary on switch. Restores factory boot image

SW2 Switch Tactile, momentary on switch

SW3 ABC Switch Three position toggle switch

SW4 ABC Switch Three position toggle switch

Loading...

Loading...