Video Input

Jetson AGX Xavier Series Product DG-09840-001_v2.5 | 91

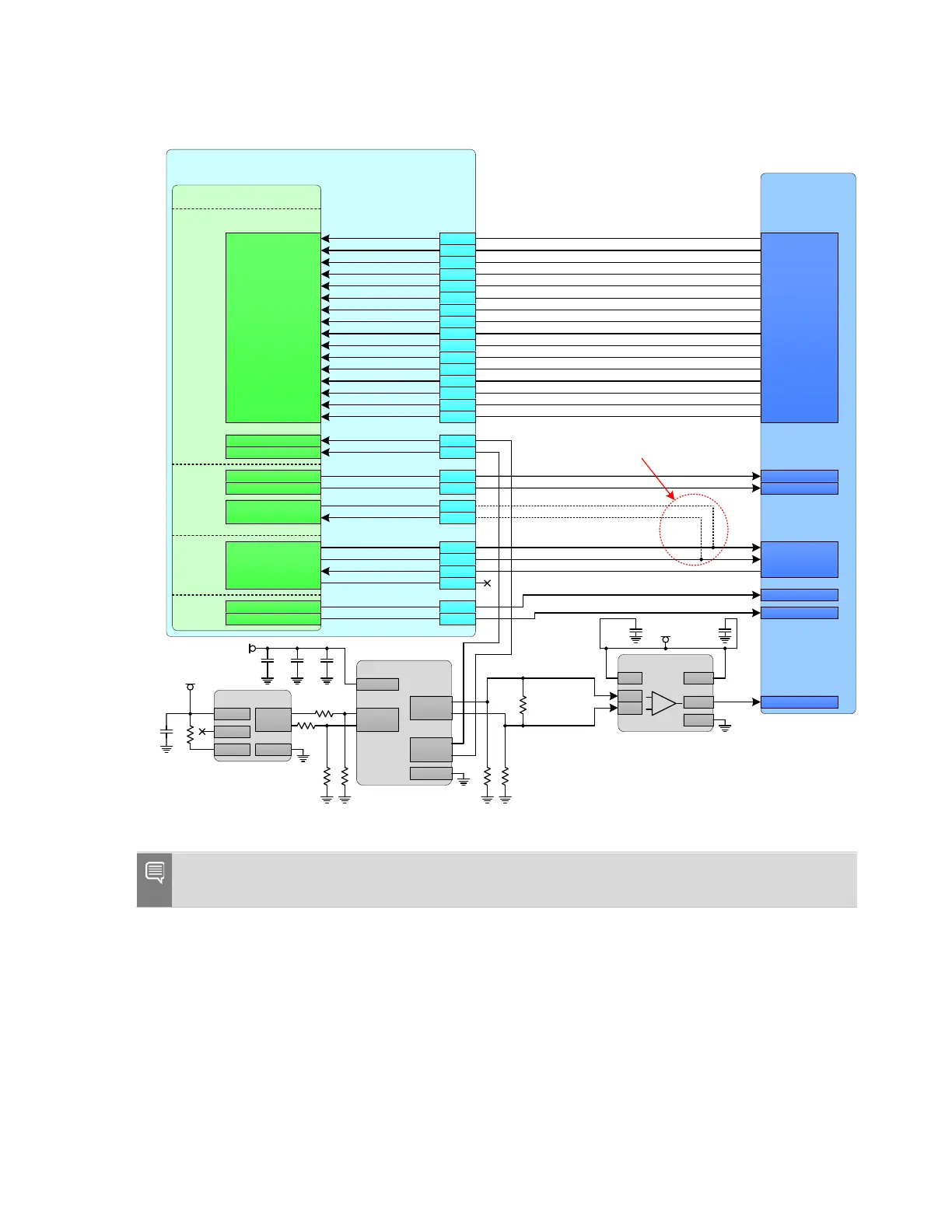

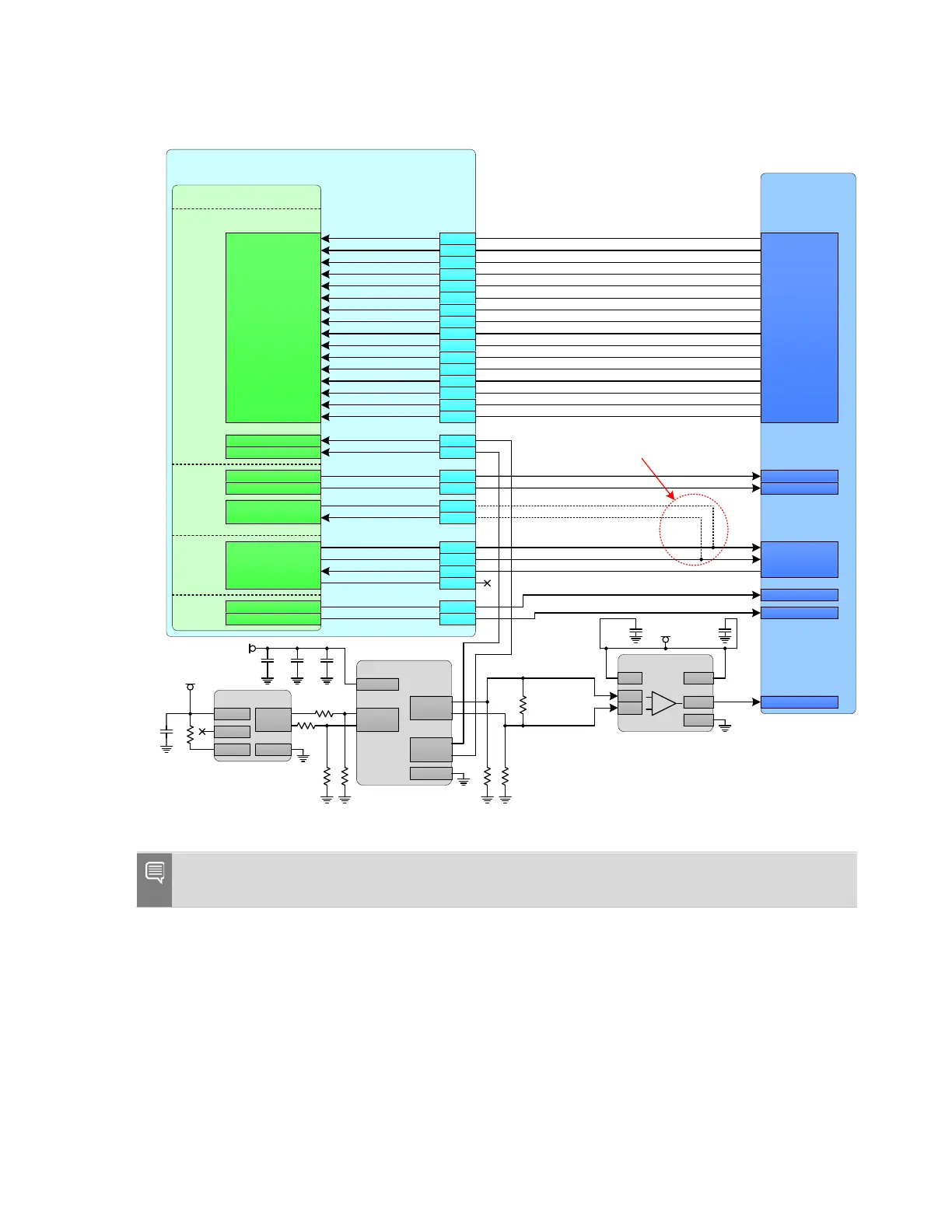

Figure 10-4. SLVS Connections

Jetson AGX Xavier

SoC - SLVS

PEX/SLVS

NVHS 0_ SLV S_ RX0 _ N

NVHS 0_ SLV S_ RX0 _ P

NVHS 0_ SLV S_ RX1 _ N

NVHS 0_ SLV S_ RX1 _ P

NVHS 0_ SLV S_ RX2 _ N

NVHS 0_ SLV S_ RX2 _ P

NVHS 0_ SLV S_ RX3 _ N

NVHS 0_ SLV S_ RX3 _ P

NVHS 0_ SLV S_ RX4 _ N

NVHS 0_ SLV S_ RX4 _ P

NVHS 0_ SLV S_ RX5 _ N

NVHS 0_ SLV S_ RX5 _ P

NVHS 0_ SLV S_ RX6 _ N

NVHS 0_ SLV S_ RX6 _ P

NVHS 0_ SLV S_ RX7 _ N

NVHS 0_ SLV S_ RX7 _ P

NVHS0_SLVS_REFCLK0_N

NVHS0_SLVS_REFCLK0_P

GP IO 18

GP IO 19

I2C3_CLK

I2C3_DAT

SP I 2_ C LK

SP I2_ MOSI

SP I2_ MI SO

SPI2_CS0_N

SP I3_ MOSI

SP I3_ MI SO

D29

D28

B2 8

B2 9

C30

C31

A31

A30

NVHS0_RX0_N

NVHS0_RX0_P

NVHS0_RX1_N

NVHS0_RX1_P

NVHS0_RX2_N

NVHS0_RX2_P

NVHS0_RX3_N

NVHS0_RX3_P

NVHS0_RX4_N

NVHS0_RX4_P

NVHS0_RX5_N

NVHS0_RX5_P

NVHS0_RX6_N

NVHS0_RX6_P

NVHS0_RX7_N

NVHS0_RX7_P

CAM

SOC_GPIO40

SPI2_SCK

SPI2_MOSI

SPI2_MISO

SPI2_CS0_N

SOC_GPIO43

CAM_I2C_SCL

CAM_I2C_SDA

C55

K56

E61

F60

D62

F53

E53

AO

SLVS

Image r/

Connector

SLVS_DX0_N

SLVS_DX0_P

SLVS_DX1_N

SLVS_DX1_P

SLVS_DX2_N

SLVS_DX2_P

SLVS_DX3_N

SLVS_DX3_P

SLVS_DX4_N

SLVS_DX4_P

SLVS_DX5_N

SLVS_DX5_P

SLVS_DX6_N

SLVS_DX6_P

SLVS_DX7_N

SLVS_DX7_P

INCK

XHS

XVS

SPI_CLK

SPI_DO

SPI_DI

Clock Buffer

VDDx

DIF0

DIF0*

CLK_IN

CLK_IN*

DIF1

DIF

1*

OSC

VCC

EN/NC

NC/EN

GND

OUTP

OUTN

10 0

Ω,1%

VDD_3 V3

10 0kΩ

15 0Ω,1%

LVDS_ 72 MHZ_P

LVDS_ 72 MHZ_N

33Ω

33Ω

49 .9Ω,1%

49 .9Ω,1%

0. 1uF

0.1uF0.1uF

0. 1 uF

VDD_3 V3

15 0Ω,1%

LVDS-CMOS

VCC

A

GND

VDD

VDD_1 V80. 1uF

B-

R

A

B*

R

GNDx

NVHS0_REFCLK_P

E30

D25

D24

B2 4

B2 5

C26

C27

A27

A26

NVHS0_REFCLK_N

E31

D60

XCE

Optional I2C option in place of SPI for imager

control. If used, dis connect Jetson AGX

Xavier SPI2_CLK & SPI 2_MOS I signals.

0. 1uF

SPI3_MOSI

G56

UART

SPI3_MISI

D56

XCLR

Note: Direct lane mapping (RX[7:0] to DX[7:0] shown in Figure 10-4. Reverse mapping (RX[7:0] to

DX[0:7]) has also been verified.

Loading...

Loading...