USB, PCIe, and UFS

Jetson AGX Xavier Series Product DG-09840-001_v2.5 | 48

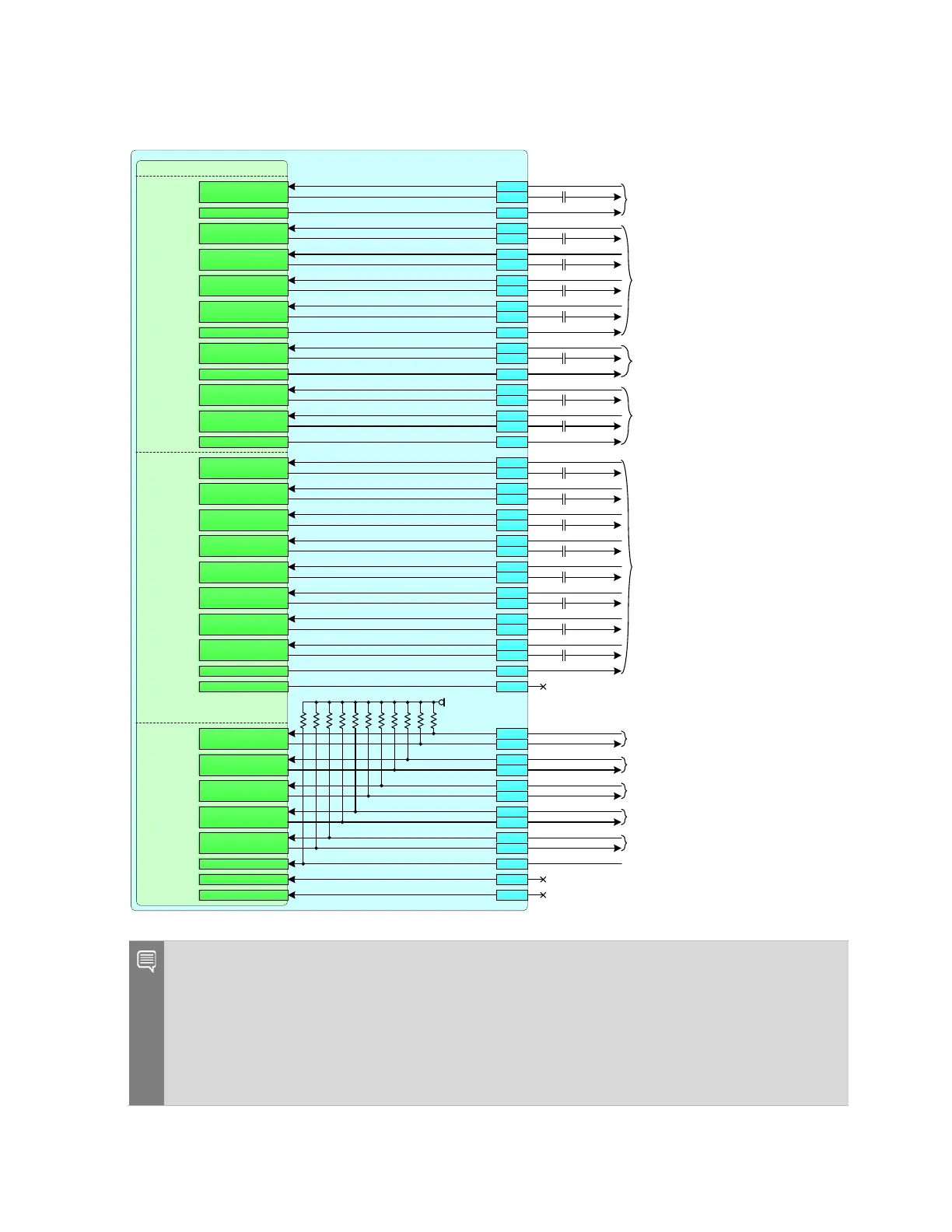

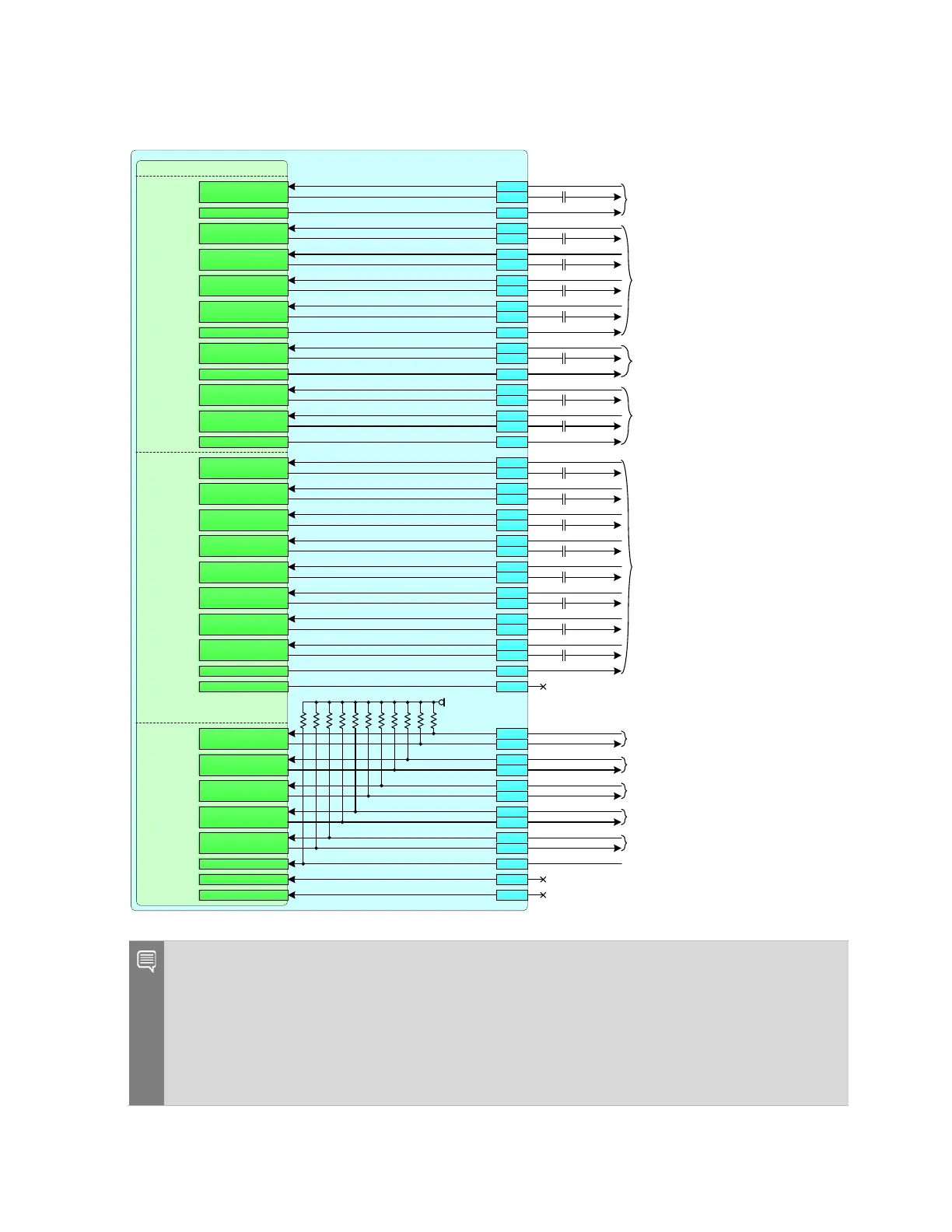

Figure 7-4. PCIe Root Port Connection Example

Jetson AGX Xavier

SoC - PCIe

PEX

PEX_L0_CLKREQ_N

PEX_L0_RST _N

PEX_L1_CLKREQ_N

PEX_L1_RST _N

PEX_WAKE_N

PEX

Control

PCIe x1 (I/F C1). Routed to eSATA

Bridge on Carrier Board.

Shared

Contr ol f or PC Ie I/F C 0

(M.2 Key M on Carrier Board)

VDDIO_AO_3V3

0. 1 uF

PEX_L3_CLKREQ_N

PEX_L3_RST _N

PEX_L5_CLKREQ_N

PEX_L5_RST _N

PEX_RX0_N/P

PEX_TX0_N/P

PEX_RX2_N/P

PEX_TX2_N/P

PEX_RX3_N/P

PEX_TX3_N/P

A23/A22

UPHY_RX0_N/P

UPHY_TX0_N/P

PEX_CLK1_N/P

UPHY_RX2_N/P

UPHY_TX2_N/P

UPHY_RX3_N/P

UPHY_TX3_N/P

UPHY_RX4_N/P

UPHY_TX4_N/P

UPHY_RX5_N/P

UPHY_TX5_N/P

PEX_CLK0_N/P

UPHY_RX7_N/P

UPHY_TX7_N/P

PEX_CLK3_N/P

UPHY_RX8_N/P

UPHY_TX8_N/P

UPHY_RX9_N/P

UPHY_TX9_N/P

PEX_CLK4_N/P

NVHS 0_SLV S_R X0 _N /P

NVHS0_TX0_N/P

NVHS 0_SLV S_R X1 _N /P

NVHS0_TX1_N/P

NVHS 0_SLV S_R X2 _N /P

NVHS0_TX2_N/P

NVHS 0_SLV S_R X3 _N /P

NVHS0_TX3_N/P

NVHS 0_SLV S_R X4 _N /P

NVHS0_TX4_N/P

NVHS 0_SLV S_R X5 _N /P

NVHS0_TX5_N/P

NVHS 0_SLV S_R X6 _N /P

NVHS0_TX6_N/P

NVHS 0_SLV S_R X7 _N /P

NVHS0_TX7_N/P

PEX_CLK5_N/P

NVHS0_SLVS_REFCLK_N/P

PEX_RX4_N/P

PEX_TX4_N/P

PEX_RX5_N/P

PEX_TX5_N/P

PEX_RX7_N/P

PEX_TX7_N/P

H17/H16

D17/D16

J23/J22

B20/B21

K20/K21

D21/D20

H21/H20

A19/A18

J19/J18

C18/C19

G18/G19

E11

D10

D9

B9

J10

K9

C8

H10

A8

PEX_CLK1_ N/P

PEX_CLK0_ N/P

PEX_CLK3_ N/P

PEX_CLK5_ N/P

F17/F16

E14/E15

F21/F20

F25/F24

PE X_L0 _ CLKREQ _N

PEX_L0_RST_N

PE X_L1 _ CLKREQ _N

PEX_L1_RST_N

PE X_L3 _ CLKREQ _N

PEX_L3_RST_N

PE X_L4 _ CLKREQ _N

PEX_L4_RST_N

PE X_L5 _ CLKREQ _N

PEX_L5_RST_N

PE X_WA K E_ N

UPHY_REFCLK1_N/P

UPHY_REFCLK2_N/P

0. 1 uF

0. 1 uF

0. 1 uF

0. 1 uF

0. 1 uF

PCIe x4 (I/F C0). Used for M.2 Key

M Connector on Carrier Board.

PCIe x1 (I/F C3). Used for M.2

Key E on Carrier Board.

PCIe x8 (I/F C5) or SLVS.

Used for PCIe x16 connector

on Car ri er Boa rd

Contr ol f or PC Ie I/F C 1

(eSATA Bridge on Carrier Board)

Contr ol f or PC Ie I/F C 3

(M.2 Key E on Carrier Board)

Contr ol f or PC Ie I/F C 5

(PCIe x16 Connector on Carrier Board)

NVHS0_RX0_N/P

NVHS0_TX0_N/P

NVHS0_RX3_ N/P

_

NVHS0_TX3_ N/P

NVHS0_RX5_ N/P

NVHS0_TX5_ N/P

NVHS0_RX4_ N/P

NVHS0_TX4_ N/P

NVHS0_RX1_N/P

NVHS0_TX1_ N/P

NVHS0_RX2_ N/P

NVHS0_TX2_ N/P

NVHS0_RX6_ N/P

NVHS0_TX6_ N/P

NVHS0_RX7_ N/P

NVHS0_TX7_ N/P

0.22uF

H25/H24

D25/D24

0.22uF

K24/K25

B24/B25

0.22uF

G26/G27

C26/C27

0.22uF

J27/J26

A27/A26

0.22uF

H29/H28

D29/D28

0.22uF

K28/K29

B28/B29

0.22uF

G30/G31

C30/C31

0.22uF

J31/J30

A31/A30

NVHS

PEX_RX8_N/P

PEX_TX8_N/P

PEX_RX9_N/P

PEX_TX9_N/P

A14/A15

J15/J14

C14/C15

G14/G15

PEX_CLK4_ N/P

E22/E23

0. 1 uF

0. 1 uF

PCIe x2 (I/F C4). Unused on

Carrier Boa rd .

PEX_L4_CLKREQ_N

PEX_L4_RST _N

G8

J9

Contr ol f or PC Ie I/F C 4

(PCIe x2 – Not used on Carrier Board)

47kΩ

4.7kΩ

47kΩ

4.7kΩ

47kΩ

4.7kΩ

47kΩ

4.7kΩ

47kΩ

4.7kΩ

47kΩ

NVHS0_REFCLK_N/P

E31/E30

For Endpoint use only

L ane 0

L ane 1

L ane 2

L ane 3

L ane 0

L ane 1

L ane 2

L ane 3

L ane 4

L ane 5

L ane 6

L ane 7

L ane 0

L ane 1

PEX_REFCLK1_N/P

E26/E27

Unus ed

PEX_REFCLK2_N/P

F29/F28

Unus ed

Notes:

• AC Capacitors required on RX lines on carrier board if connected directly to device. They are

not placed on the carrier board if connected to a PCIe connector. In that cases, the AC caps are

on the PCIe add-in board.

• See design guidelines for correct AC capacitor values.

• The PCIe REFCLK inputs and PCIEx_CLK clock outputs comply to the PCIe CEM specification

“REFCLK DC Specifications and AC Timing Requirements.” The clocks are HCSL compatible.

Loading...

Loading...