Jetson AGX Xavier Series Product DG-09840-001_v2.5 | 37

Chapter 7. USB, PCIe, and UFS

Jetson AGX Xavier facilitates multiple high-speed interfaces to be brought out on the module

in different configurations. The tables show the configurations that have been used on the

developer kit.

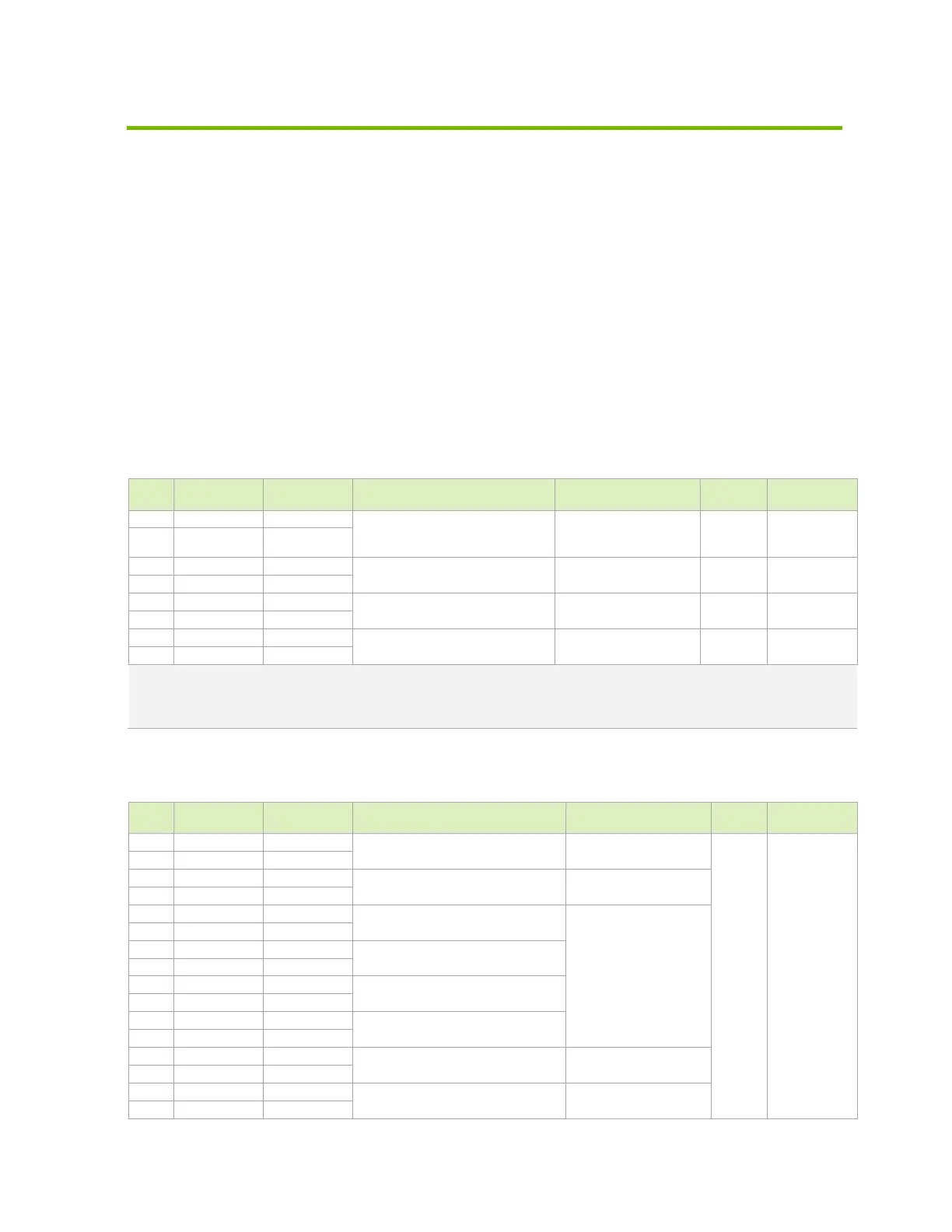

Table 7-1. USB 2.0 Pin Descriptions

Pin # Module Pin

Name

SoC Signal Usage/Description Usage on NVIDIA Carrier

Board

Direction Pin Type

F13 USB0_N USB0_DN USB 2.0 Port 0 Data

UART-USB Bridge or USB

Type C Connector (J512)

Bidir

USB2 Diff pair

F12 USB0_P USB0_DP

C10 USB1_N USB1_DN USB 2.0, Port 1 Data

USB Type C Connector (J513)

Bidir

USB2 Diff pair

A11 USB2_N USB2_DN USB 2.0, Port 2 Data

M.2 Key E Connector

Bidir

USB2 Diff pair

A10 USB2_P USB2_DP

G10 USB3_N USB3_DN USB 2.0, Port 3 Data

USB / eSATA Connector (USB

2.0)

Bidir USB2 Diff pair

G11 USB3_P USB3_DP

Notes:

1. In the Type/Dir column, Output is from Jetson AGX Xavier. Input is to Jetson AGX Xavier. Bidir is for Bidirectional

signals.

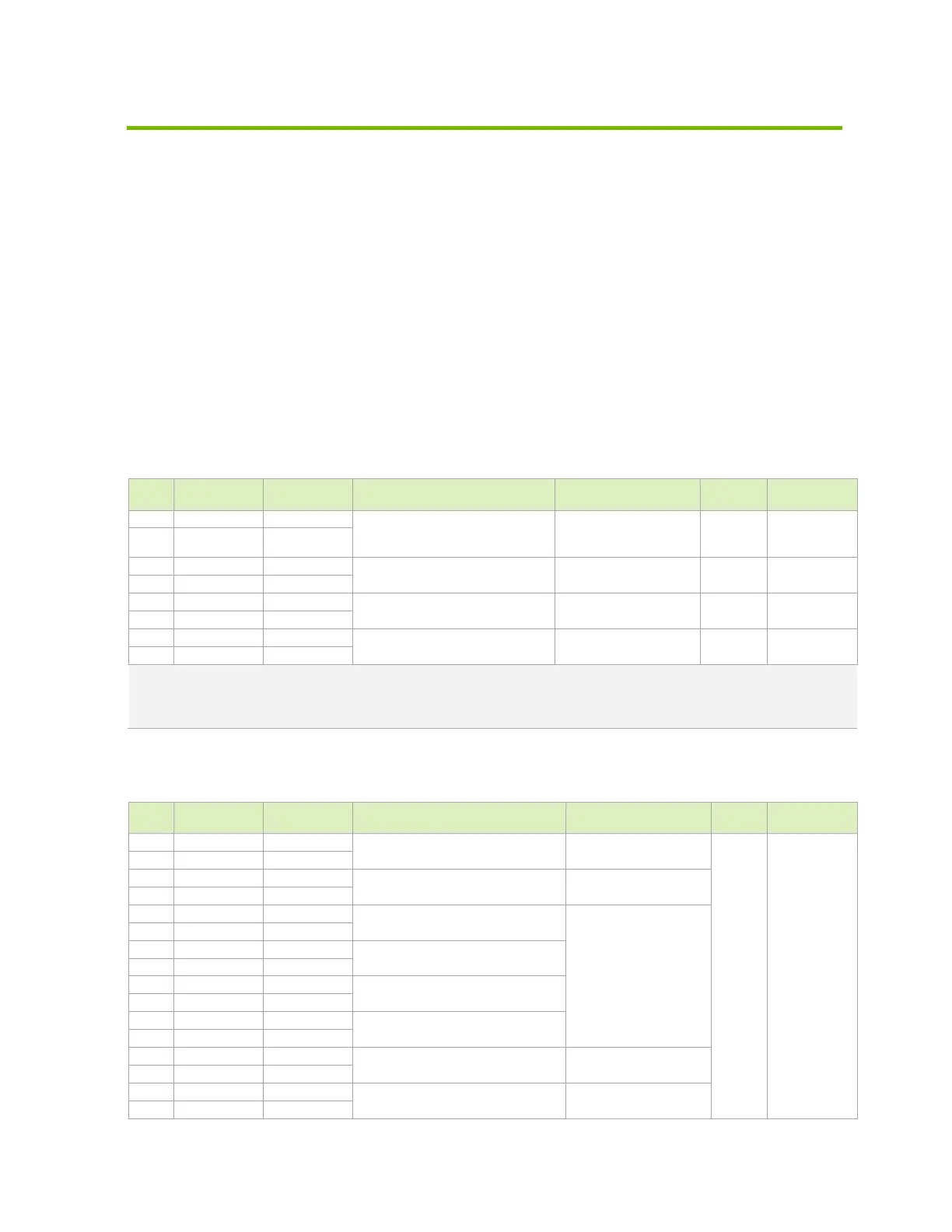

Table 7-2. UPHY Data Lane Pin Descriptions USB 3.1, PCIe, and UFS

Pin # Module Pin

Name

SoC Signal Usage/Description Usage on NVIDIA Carrier

Board

Direction Pin Type

A23 UPHY_RX0_N PEX_RX0_N UPHY Receive 0. PCIe x1 controller #1. eSATA Bridge Input UPHY Diff Pair

A22 UPHY_RX0_P PEX_RX0_P

UPHY Receive 1. USB 3.1 port 2. USB Type C Alt Mode Switch

#1

C23 UPHY_RX1_P PEX_RX1_P

B20 UPHY_RX2_N PEX_RX2_N UPHY Receive 2. PCIe x4 controller #0,

lane 0.

M.2 Key M Connector

B21 UPHY_RX2_P PEX_RX2_P

D21 UPHY_RX3_N PEX_RX3_N UPHY Receive 3. PCIe x4 controller #0,

lane 1.

D20 UPHY_RX3_P PEX_RX3_P

A19 UPHY_RX4_N PEX_RX4_N UPHY Receive 4. PCIe x4 controller #0,

lane 2.

A18 UPHY_RX4_P PEX_RX4_P

C18 UPHY_RX5_N PEX_RX5_N UPHY Receive 5. PCIe x4 controller #0,

lane 3.

C19 UPHY_RX5_P PEX_RX5_P

B17 UPHY_RX6_N PEX_RX6_N UPHY Receive 6. USB 3.1 port 0.

USB Type C Alt Mode Switch

#2

B16 UPHY_RX6_P PEX_RX6_P

D17 UPHY_RX7_N PEX_RX7_N UPHY Receive 7. PCIe x1 controller #3. M.2 Key E Connector

D16 UPHY_RX7_P PEX_RX7_P

Loading...

Loading...