Jetson AGX Xavier Series Product DG-09840-001_v2.5 | 34

Chapter 6. General Routing Guidelines

6.1 Signal Name Conventions

The following conventions are used in describing the signals for Jetson AGX Xavier:

Signal names use a mnemonic to represent the function of the signal. For example,

Secure Digital Interface #3 Command signal is represented as SDCARD_CMD, written in

bold to distinguish it from other text. All active low signals are identified by a # or an

underscore followed by capital N (_N) after the signal name. For example, RESET_IN#

indicates an active low signal. Active high signals do not have the underscore-N (_N) after

the signal names. For example, SDCARD_CMD indicates an active high signal. Differential

signals are identified as a pair with the same names that end with _P and _N, just P and N

or + and - (for positive and negative, respectively). For example, USB1_DP and USB1_DN

indicate a differential signal pair.

I/O Type The signal I/O type is represented as a code to indicate the operational

characteristics of the signal. The following table lists the I/O codes used in the signal

description tables.

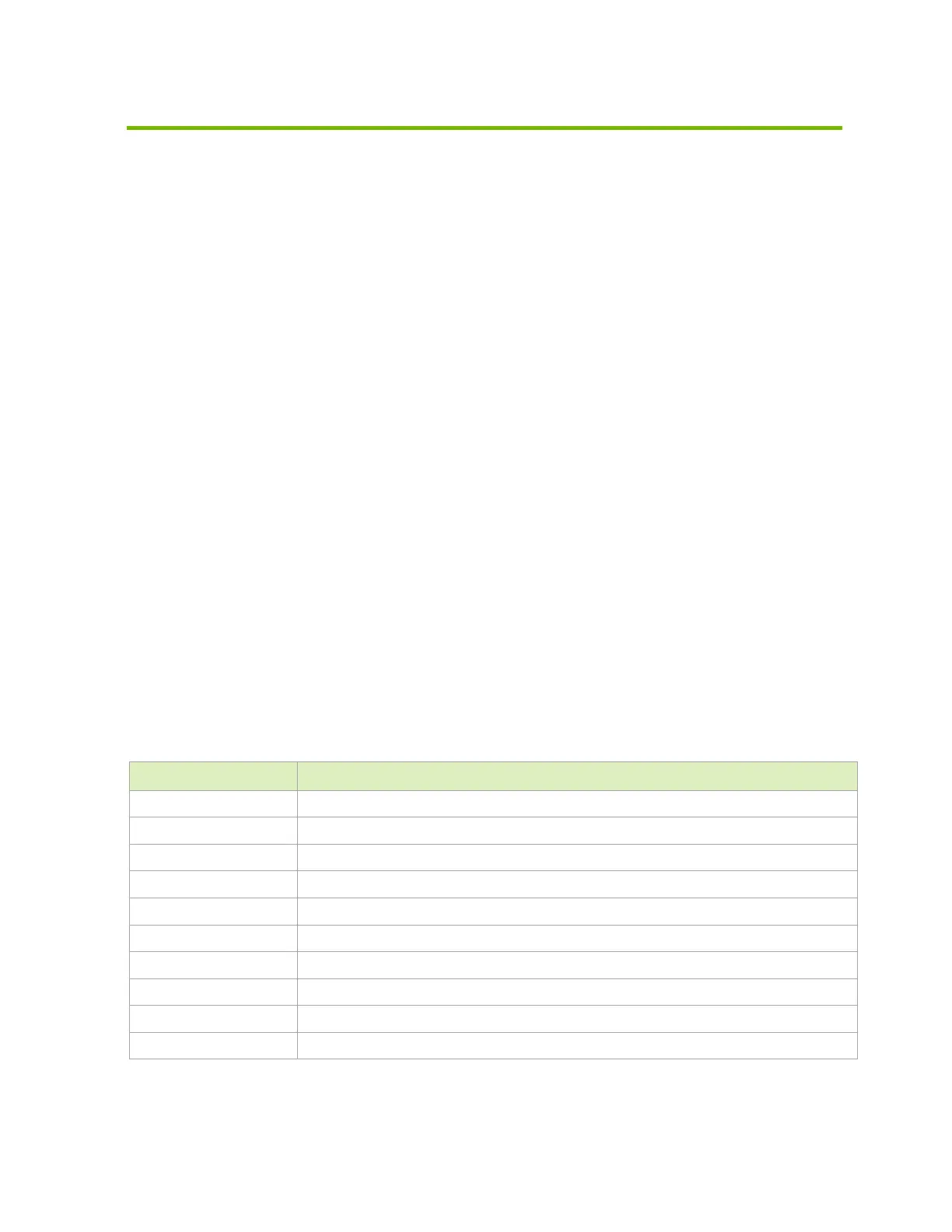

Table 6-1. Signal Type Codes

Code Definition

Analog

Bidirectional Differential Input/Output

Differential Input

Differential Output

Bidirectional Input/Output

Input

Output

Open Drain Output

Bidirectional Input / Open Drain Output

Power

Loading...

Loading...