percent of the global parameter UBase. To avoid oscillations of the output START

signal, a hysteresis has been included.

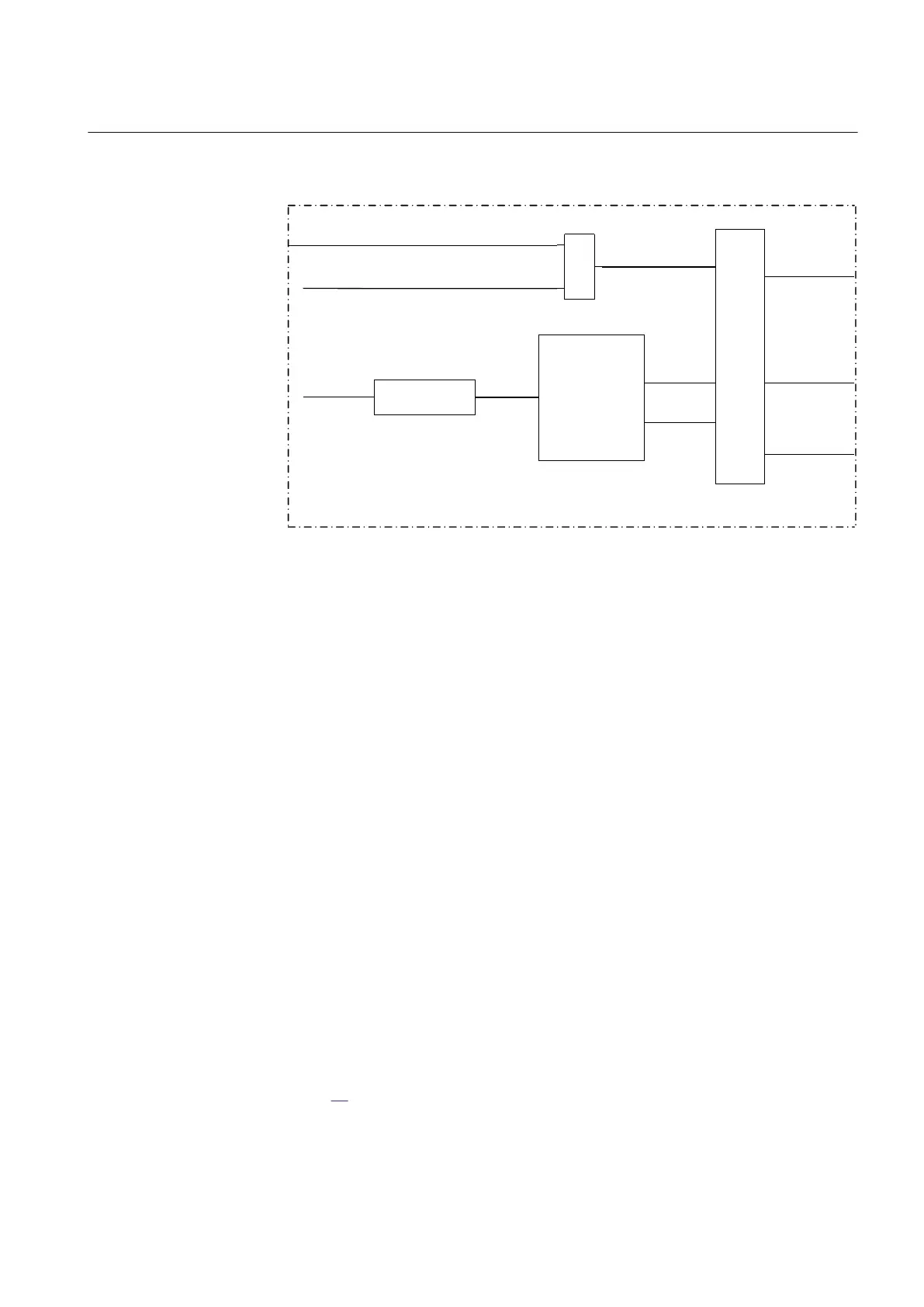

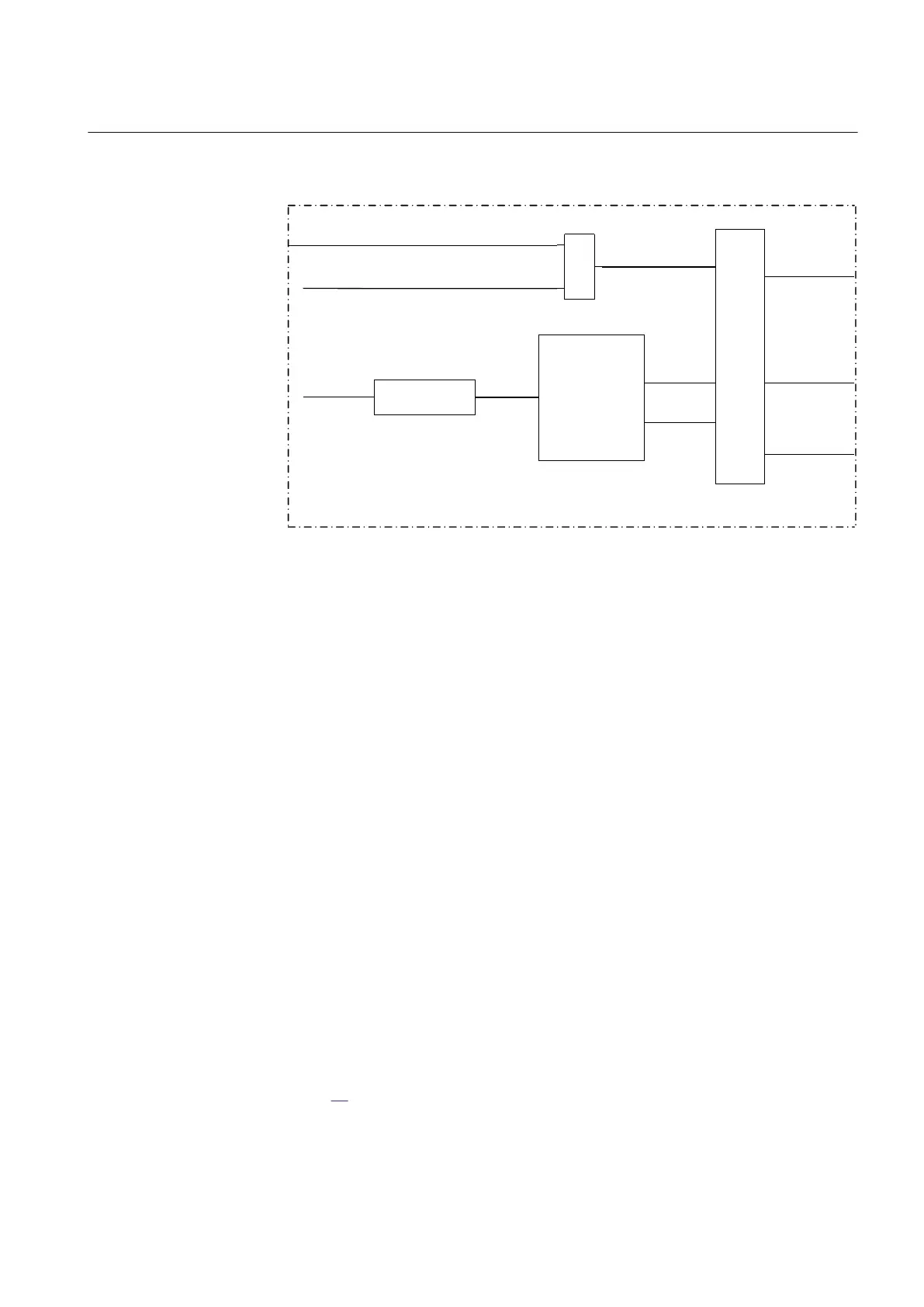

START

START

TRIP

Start

&

Trip

Output

Logic

Definite Time Delay

TimeDlyOperate

BLOCK

IEC09000033-1.vsd

Frequency Comparator

f > StartFrequency

TRIP

BLKDMAGN

BLOCK

OR

freqNotValid

IEC09000033 V1 EN

Figure 82: Schematic design of overfrequency protection SAPTOF

8.2.7.2 Time delay

The time delay for SAPTOF is a settable definite time delay, specified by the setting

tDelay.

If the START condition frequency ceases during the delay time, and is not fulfilled

again within a defined reset time, the START output is reset.

8.2.7.3 Blocking

It is possible to block Over frequency protection (SAPTOF) completely, by binary

input signals or by parameter settings, where:

BLOCK:

blocks all outputs

If the measured voltage level decreases below the setting of MinValFreqMeas in the

preprocessing function both the START and the TRIP outputs are blocked.

8.2.7.4 Design

The design of overfrequency protection SAPTOF is schematically described in

figure 82.

1MRK 511 287-UEN A Section 8

Frequency protection

185

Technical manual

Loading...

Loading...