Jetson AGX Xavier Series Product DG-09840-001_v2.5 | v

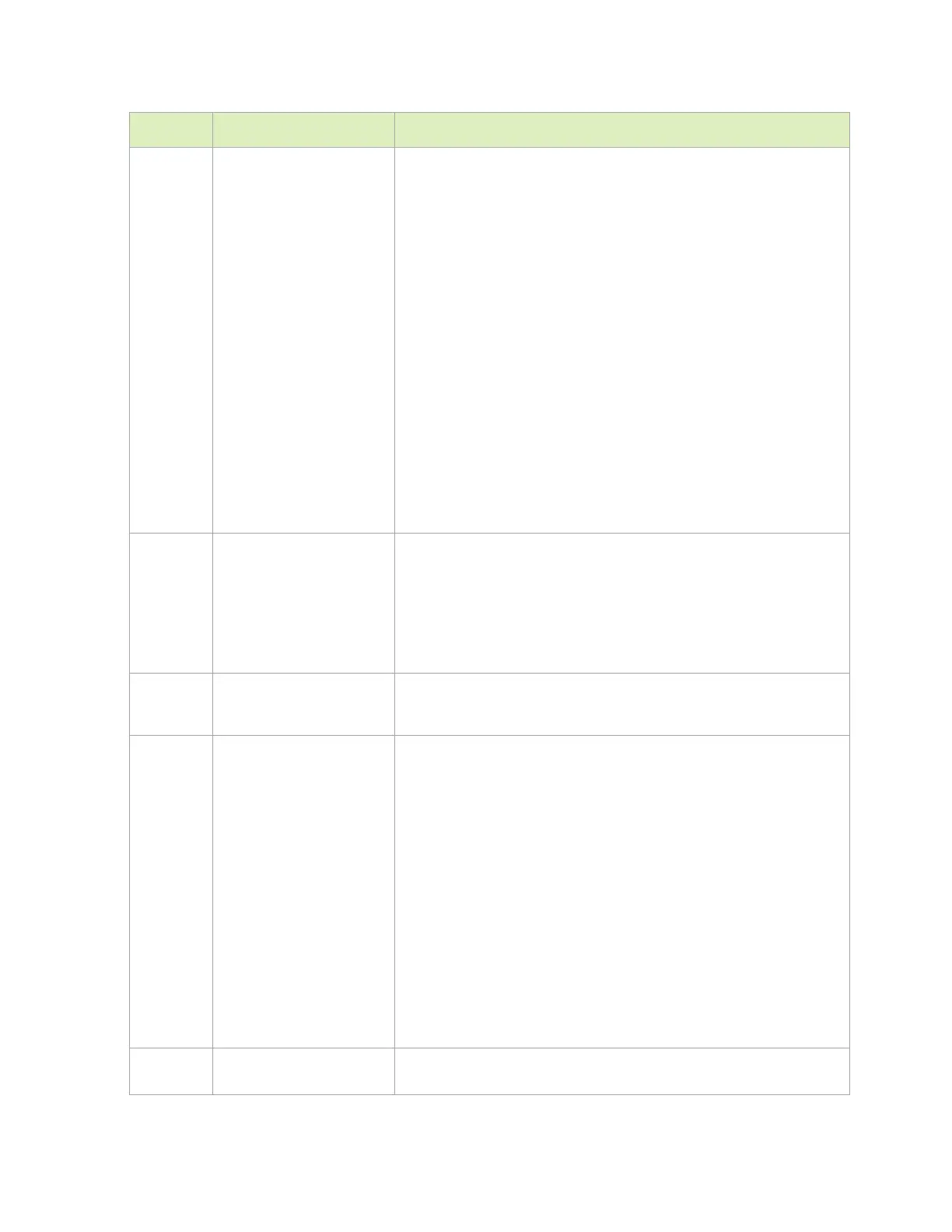

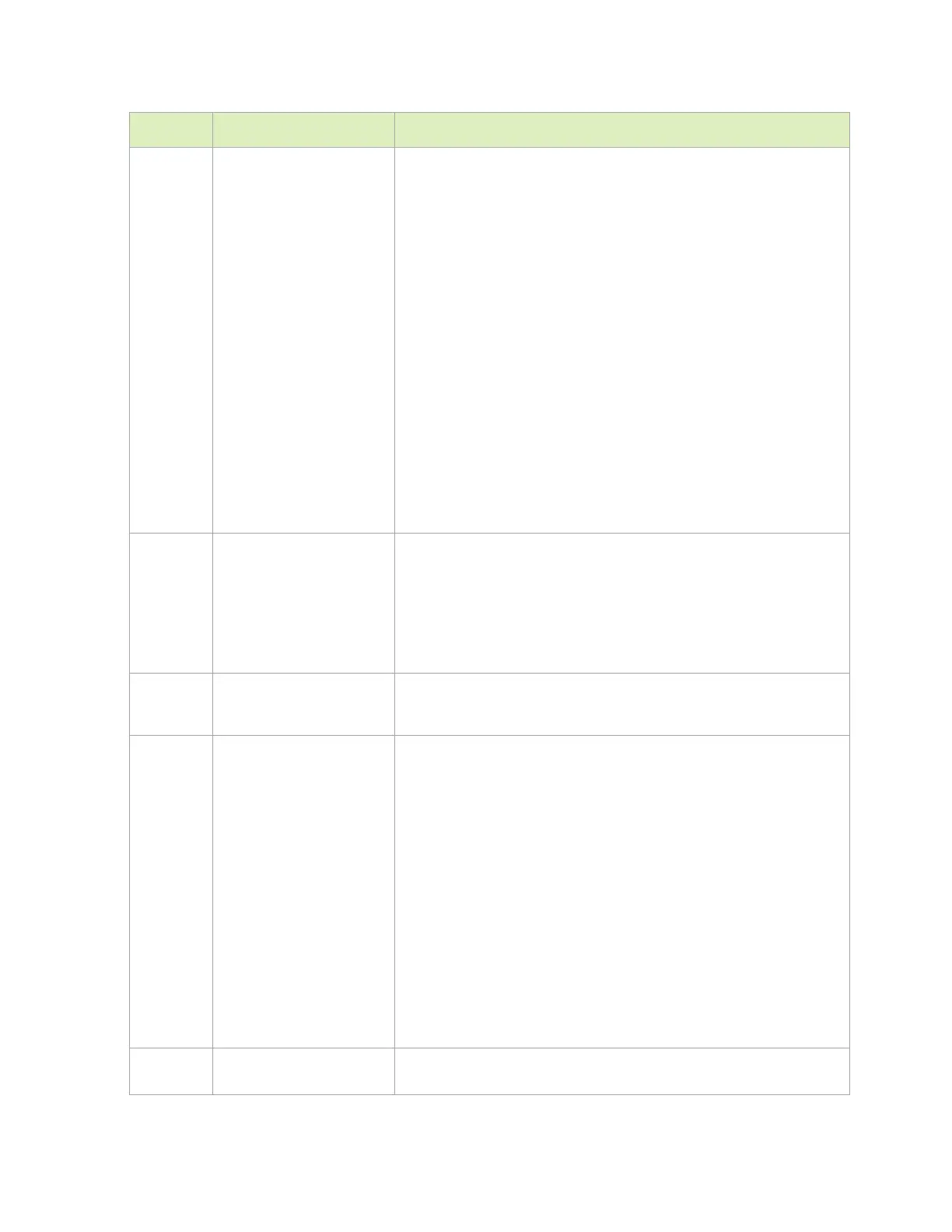

Version Date Description of Change

• Added NVHS0_SLVS_REFCLK_N/P and PEX_WAKE_No pins

to Table 7-15

• Added load switch on 3.3V to eDP/DP connector in Figure 9-1

• Updated Figure 9-3 to show load switch providing 5V to the

connector and added related note

• Removed mention of debug and added note in Table 13-10

• Removed mention of debug connector and changed UART2

connection on CB to UART USB bridge in Figure 13-7

• Added Section 15.1 “USB Recovery Mode”

• Removed UART2 as debug UART and removed related note

in Figure 15-1

• Replaced example showing UART2 with one showing UART3

instead and removed note in Figure 15-2

• Removed mention of UART2 in Section 15.2.2 and the table

listed in the section

• Added bring-up checklist to the attachments and listed in

Chapter 18

2.2 November 18, 2020 • Added notes to Figure 5-3, Figure 5-4, and Figure 7-3

• Added note to clarify PCIe clock output and RFCLK input

signaling type to Figure 7-4

• Added insertion loss S-parameter plot figure (Figure 7-6)

• Updated Table 10-5 based on new guidelines from IOSI

based on improved model

2.3 January 28, 2021 • Updated to include Jetson AGX Xavier Industrial (JAXi)

• Updated pin description attachment

2.4 June 8, 2021 • Attachment: Updated pin description Excel file

• Module spacing: Updated Section 3.3: Module to Carrier

Board Standoff Height Recommendations

Updated mating connector spacing tolerance and column

titles/spacing numbers in Table 3-1 and Table 3-2

• Updated STANDBY_ACK_N description in Table 5-1: Power,

System, and Thermal Pin Descriptions.

• PCIE: Table 7-4: PCIe Clock and Control Pin Descriptions;

updated CLKREQ, RST and WAKE pin descriptions.

• USB: Updated Figure 7-1: Simple USB Type A Connection

Example.

• I2S: Updated Table 12-1: Jetson AGX Xavier Audio Pin

Description to indicate I2S6 (DAP6 on SoC) is not supported

for JAXi.

2.5 December 2, 2021 • Corrected Table 2-2 (Pinout Matrix) to have GPIO12 (pin E10)

called out for Safety MCU usage

Loading...

Loading...