7.3 Processor Unit: RPU-013

7-35

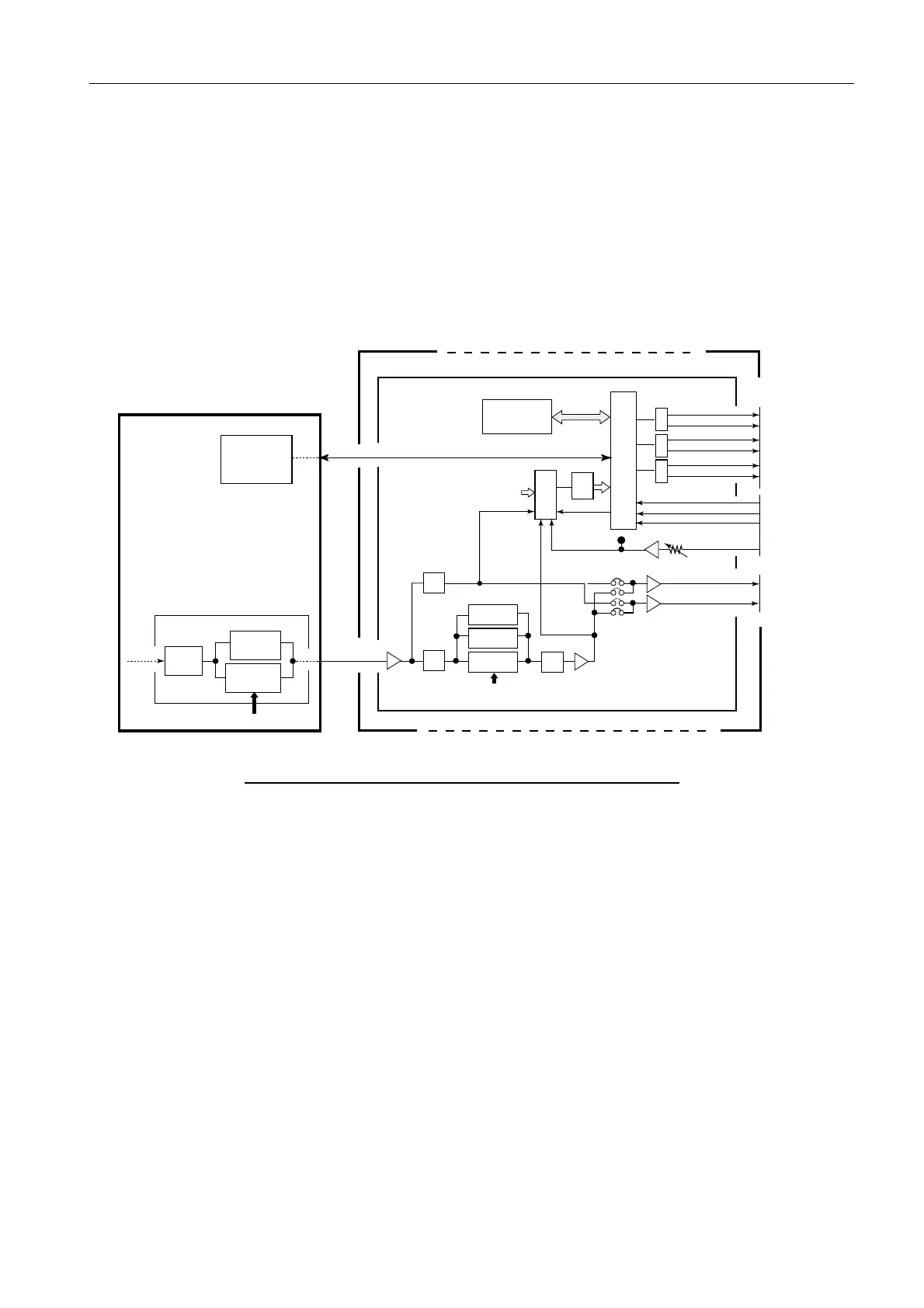

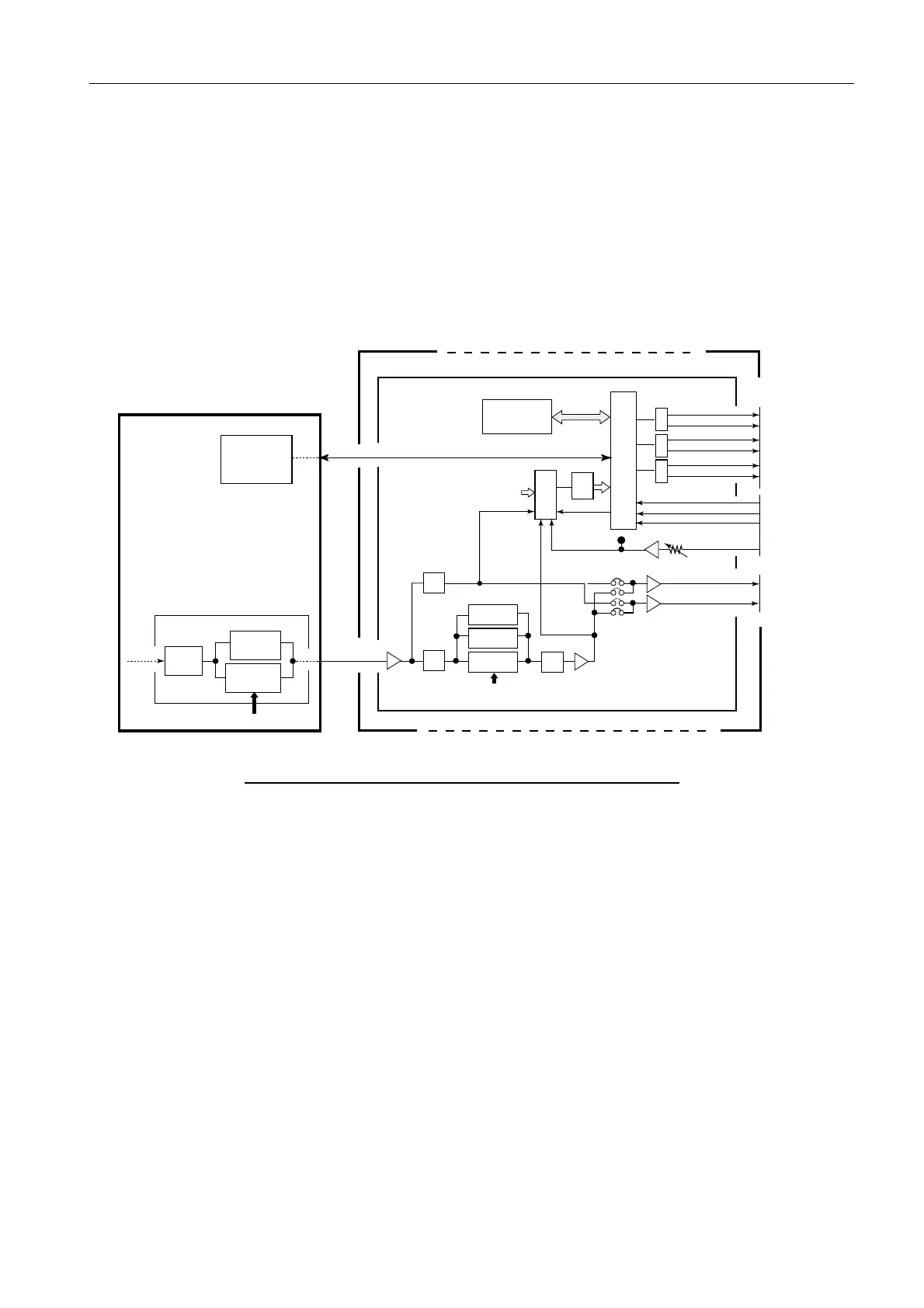

2. IF-VIDEO MIX signal input

IF-VIDEO MIX signals in which video signals and 60 MHz IF signals from the TR unit

are superimposed and separated at HPF (30 MHz)/LPF (30 MHz), and outputted as

external monitor signals of Slave-Display-1 and Slave Display-2.

Slave-Display-1 is set as Full-Log signal and Slave Display-2 as Semi-Log signal but

the jumper setting of JP3 to JP6 can change the setting. Video signals are converted into

A/D (8bit) at U46 in the next stage and inputted to the U46, SPU FPGA.

Fig. 7.3.7 Input of IF-VIDEO MIX signal to the SPU board

The level of video signal from external radar can be adjusted by R401 so that the video

signal level of TP58 becomes 2.0 Vp-p.

See page.4-74 to 4-82 for information on connection of video signals to and from

external devices.

RF unit

IF + Video MIX

U46

SPU FPGA

RF Tx/Rx

BP

HD

TRIG

U30

U41

U40

OP HD OUT-1

HD IN

TRIG IN

BP IN

OP VIDEO OUT-1 (FULL LOG)

OP VIDEO OUT-2 (SEMI LOG)

SEMI LOG VIDEO

OP HD OUT-2

OP BP OUT-1

OP BP OUT-2

OP TRIG OUT-1

OP TRIG OUT-2

FULL LOG OUT

Log AMP

(Video sig.)

IF AMP

(Liner: 60MHz)

IF AMP

(60MHz)

IF input

IF AMP p.c.b

LPF

(L/C)

HPF

(L/C)

Long Puls FIL

(BW: 2.5MHz)

MIdle Puls FIL

(BW: 10MHz)

Short Puls FIL

(BW: 35MHz)

DET

(U86)

U85

U78

U78

U87

JP3

JP4

JP5

JP6

BW A/B sel

TEST ECHO

SEL

(U83)

A/D

(U76)

U85

OP VIDEO IN

OP VIDEO IN

R401

SEL VIDEO

8bit

ARPA/MAIN CPU

Echo data

RPU-013

RFC p.c.b

SPU p.c.b

J616

Master Radar

J617, J618

SUB Display-1, 2

J617, J618

SUB Display-1, 2

MIX

AD/DATA

TP58

GAIN/STC CONT

Loading...

Loading...