10

FUNCTIONS AND PROGRAMMING

10.3 Programming Using MELSEC Data Link Functions

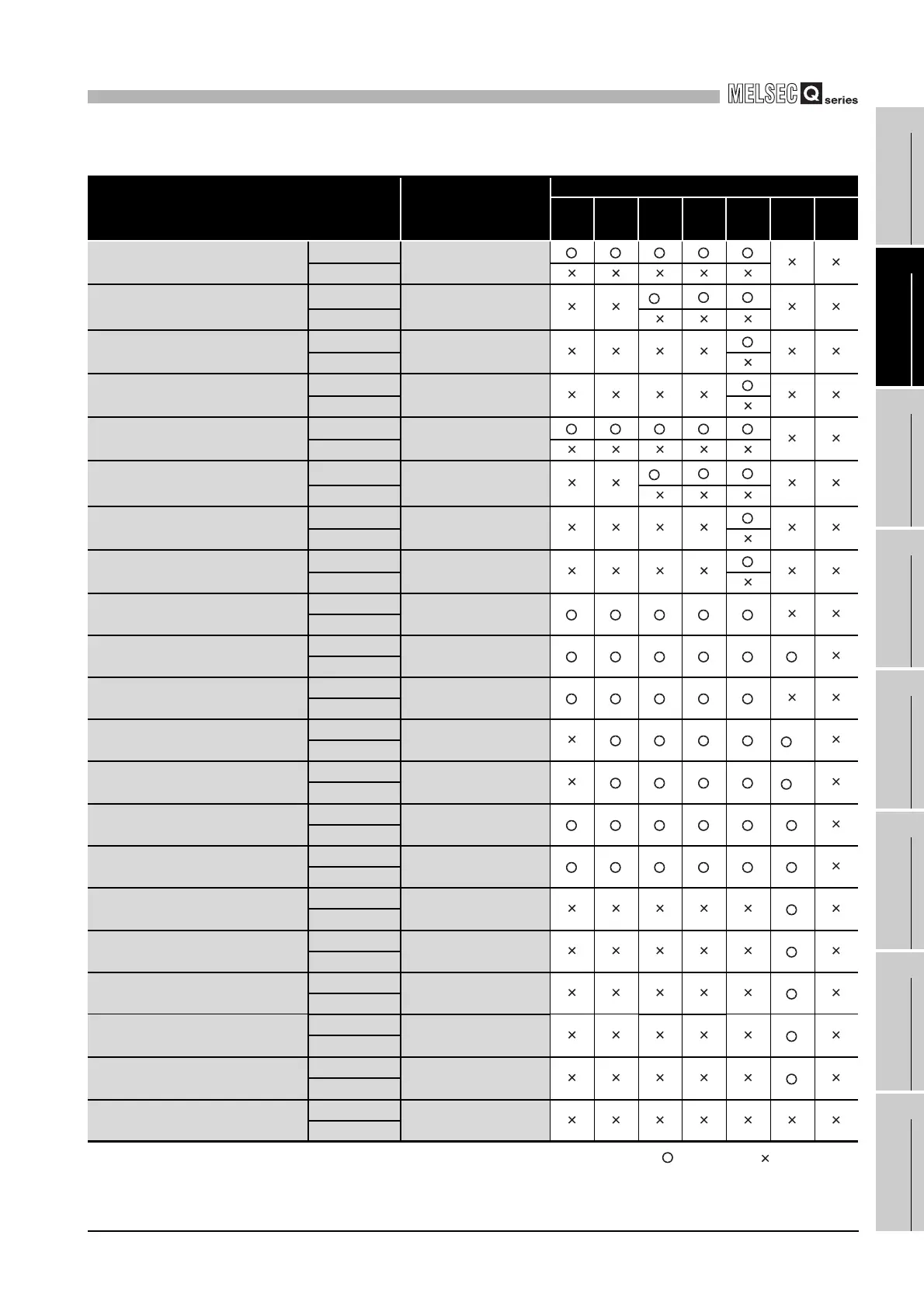

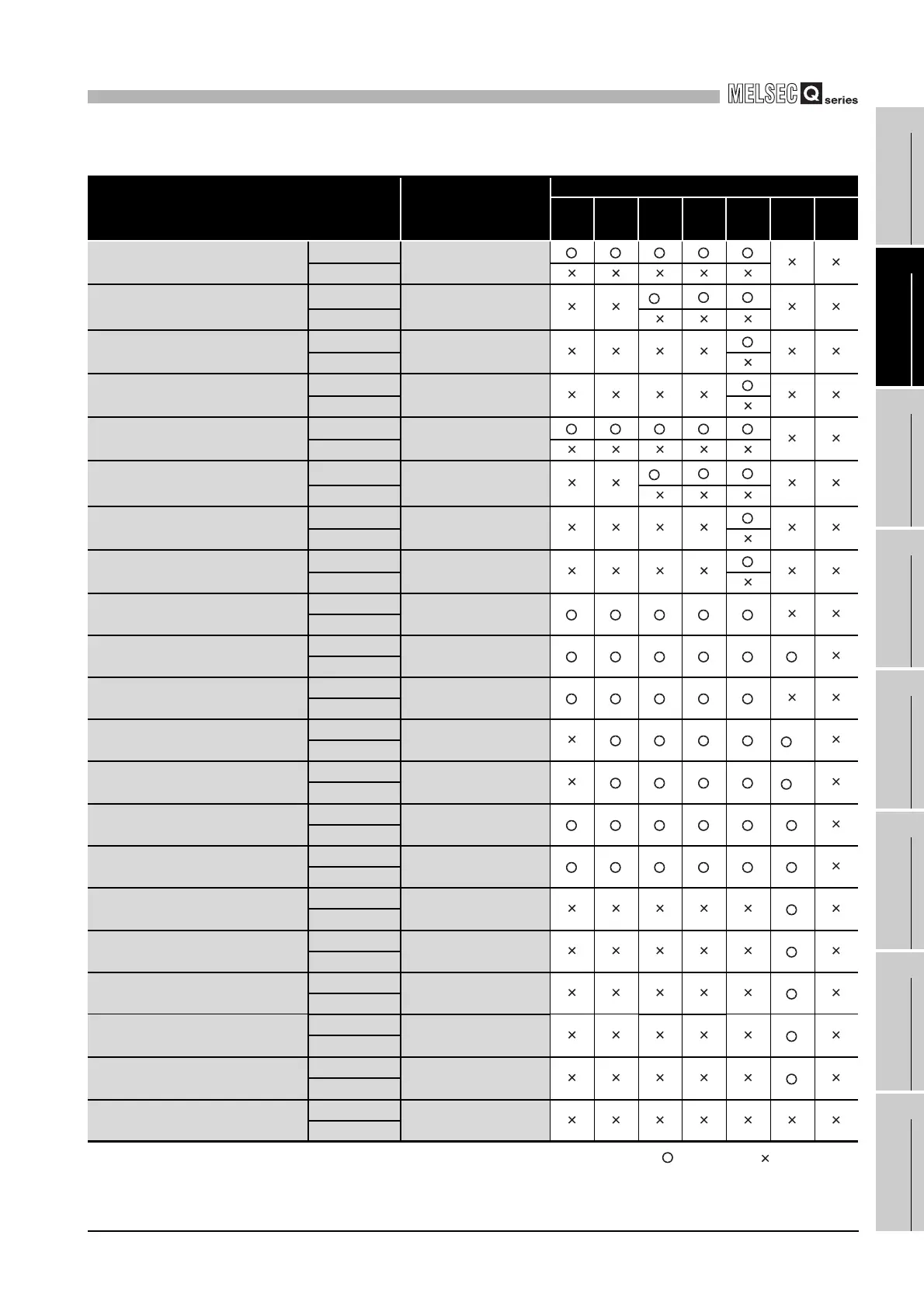

10.3.12 Accessible ranges and devices of MELSEC data link functions

10 - 54

9

UTILITY OPERATION

10

FUNCTIONS AND

PROGRAMMING

11

OVERVIEW OF

MULTIPLE CPU

SYSTEM

12

MULTIPLE CPU

SYSTEM

CONFIGURATION

13

MULTIPLE CPU

SYSTEM

CONCEPT

14

COMMUNICATIONS

BETWEEN CPU

MODULES

15

PARAMETERS

ADDED FOR

MULTIPLE CPU

16

PRECAUTIONS FOR

USE OF AnS SERIES

MODULE

: Accessible, : Inaccessible

* 1 Access is not allowed in the case of the A2ACPU(-S1).

* 2 Access is not allowed in the case of the Q00JCPU.

(To next page)

Table10.24 Accessible devices at the time of other station access(Continued)

Device

Device type

(Device name

specification)

Access target

1) 2) 3) 4) 5) 6) 7)

T (setting value main)

Batch

DevTM

Random

T (setting value sub 1)

Batch

DevTS

*1

Random

T (setting value sub 2)

Batch

DevTS2

Random

T (setting value sub 3)

Batch

DevTS3

Random

C (setting value main)

Batch

DevCM

Random

C (setting value sub 1)

Batch

DevCS

*1

Random

C (setting value sub 2)

Batch

DevC2

Random

C (setting value sub 3)

Batch

DevC3

Random

A

Batch

DevA

Random

Z

Batch

DevZ

Random

V (index register)

Batch

DevV

Random

R (file register)

Batch

DevR

*2

Random

ER (extension file register)

Batch DevER(0) to

DevER(256)

*2

Random

B

Batch

DevB

Random

W

Batch

DevW

Random

Q/QnA link special relay

(within the Q/QnACPU)

Batch

DevQSB

Random

Retentive timer (contact)

Batch

DevSTT

Random

Retentive timer (coil)

Batch

DevSTC

Random

Q/QnA link special register

(within the Q/QnACPU)

Batch

DevQSW

Random

Q/QnA link edge relay

(within the Q/QnACPU)

Batch

DevQV

Random

Own station random access buffer

Batch

DevMRB

Random

Loading...

Loading...