14

COMMUNICATIONS BETWEEN CPU MODULES

14.3 Data Communications Using CPU Shared Memory

14.3.1 CPU shared memory structure

14 - 10

9

UTILITY OPERATION

10

FUNCTIONS AND

PROGRAMMING

11

OVERVIEW OF

MULTIPLE CPU

SYSTEM

12

MULTIPLE CPU

SYSTEM

CONFIGURATION

13

MULTIPLE CPU

SYSTEM

CONCEPT

14

COMMUNICATIONS

BETWEEN CPU

MODULES

15

PARAMETERS

ADDED FOR

MULTIPLE CPU

16

PRECAUTIONS FOR

USE OF AnS SERIES

MODULE

14.3.1 CPU shared memory structure

The following indicates the CPU shared memory structure and accessibility of the C

Controller module.

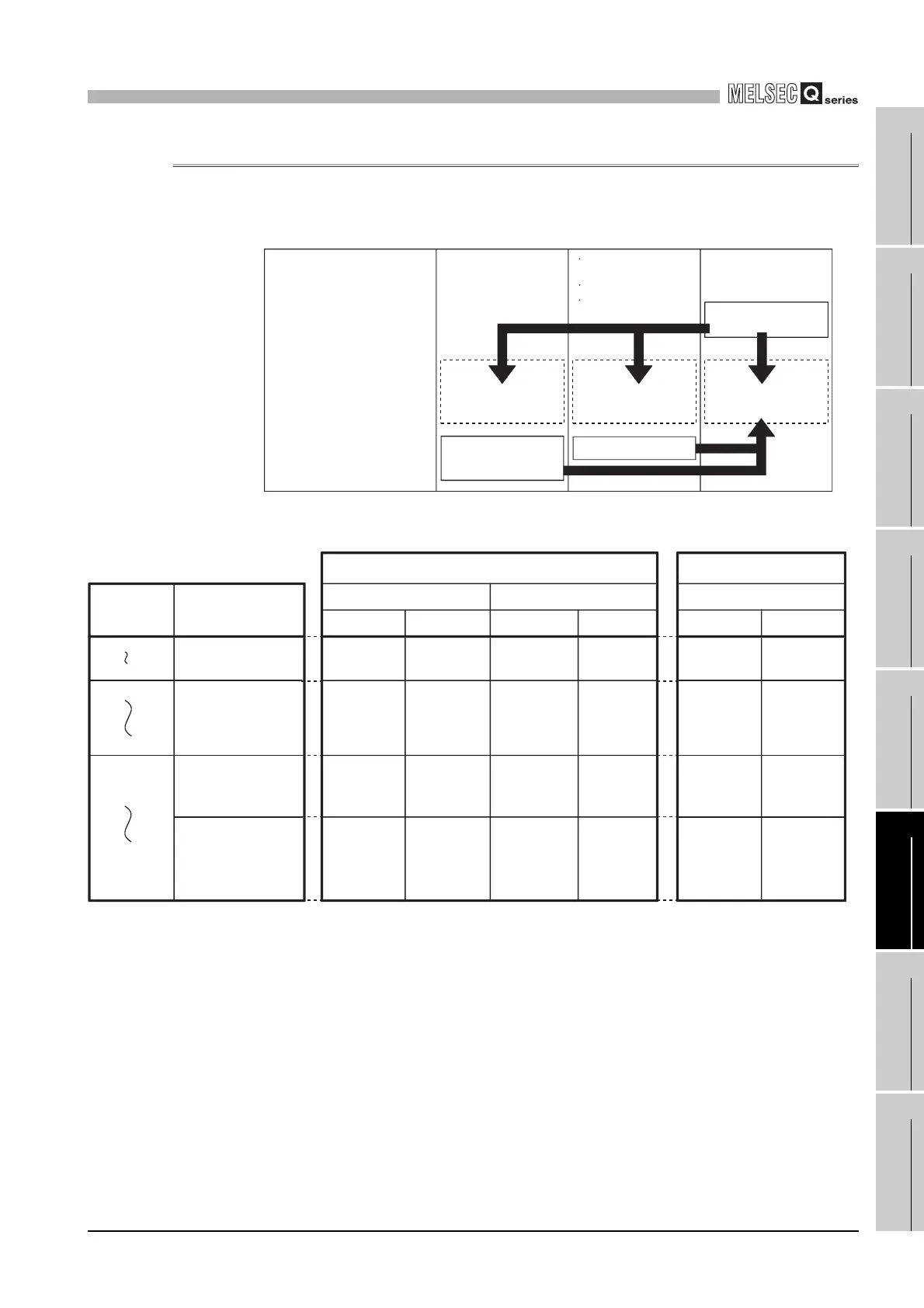

Figure 14.6 Access diagram

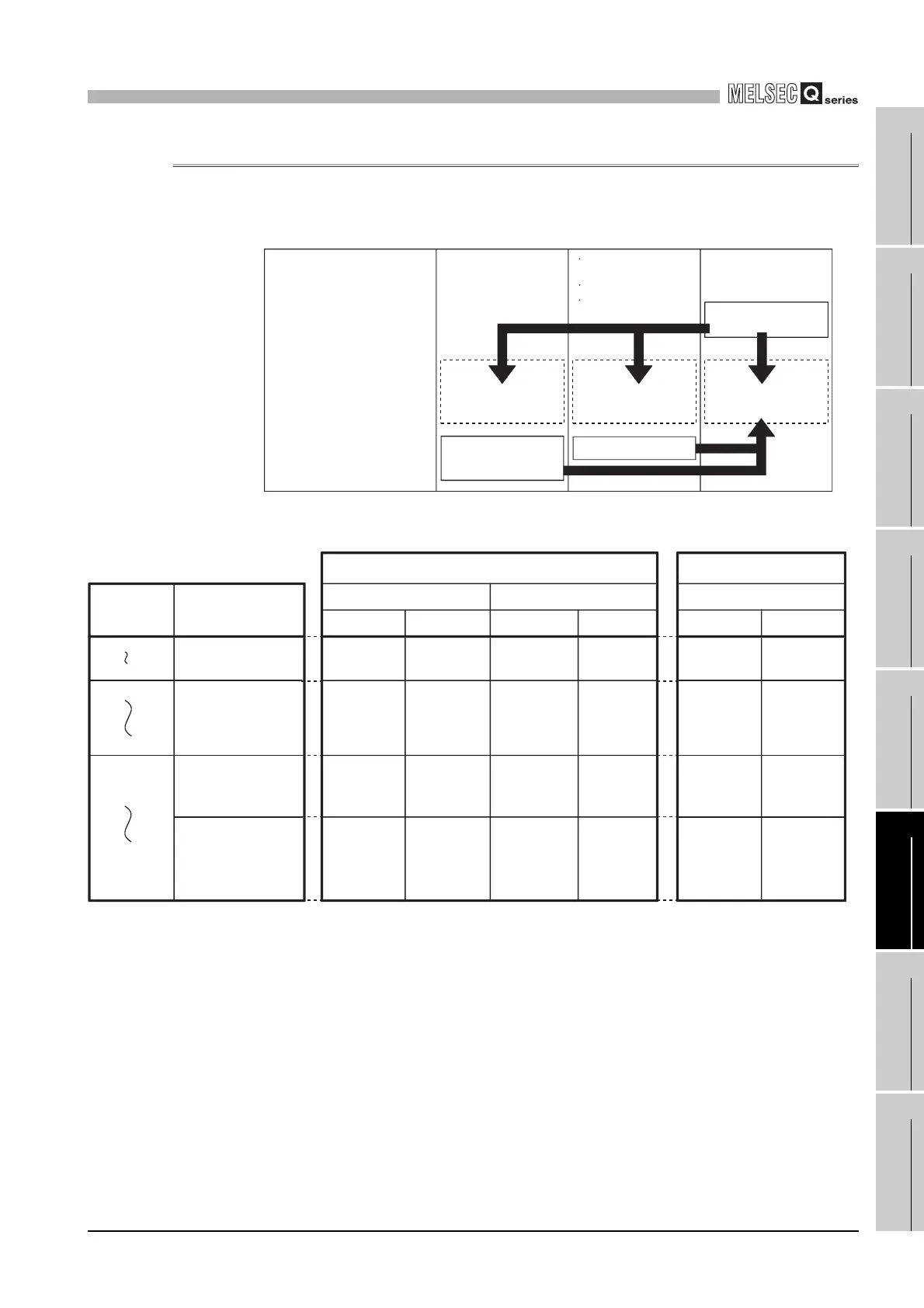

Figure 14.7 Accessibility table

Power supply

Programmable

controller CPU

Motion CPU

C Controller module

(another CPU)

C Controller module

(host CPU)

User program

CPU shared memory

of another CPU

CPU shared memory

of host CPU

2)

CPU shared memory

of another CPU

1)

3)

Programmable

controller CPU

Sequence

program

2)

Program

Host CPU operation

information area

System area

Auto refresh area

User free area

Address

0

H (0H)

200H (60H)

800

H (C0H)

FFF

H (1FFH)

1FF

H (5FH)

7FF

H (BFH)

Access to host CPU 1)

Access to another CPU 2)

Write Write

Enabled

Enabled

Disabled

Disabled

Enabled Disabled Enabled

Disabled Disabled Enabled

Enabled

Disabled

Enabled

Enabled Disabled

Enabled

Disabled Enabled

Disabled Enabled

Disabled

Enabled

Disabled

Enabled

Write

*2

*1, *6

Read

*5

*1

*2

*3

*4

*5

*6

Area name

Access from host CPU

Access to host CPU 3)

Access from another CPU

Use the QBF ToBuf function to write data to the auto refresh area and user free area of the host CPU (C Controller module).

Indicates the address of the CPU shared memory.

Refer to the manual of the corresponding CPU module for how to make access from the programmable controller CPU/Motion CPU of

When CPU No. 1 is the Basic model QCPU, the address of the CPU shared memory is the value within the parentheses.

Use the QBF FromBuf function to read data from the host CPU operation information area, auto refresh area, and user free area of the

host CPU (C Controller module).

Use the QBF FromBuf function to read data from the host CPU operation information area, auto refresh area, and user free area of

another CPU (Programmable controller CPU, Motion CPU).

Read

*3

Read

*4

Loading...

Loading...