RL78/G1H CHAPTER 9 REAL-TIME CLOCK

R01UH0575EJ0120 Rev. 1.20 Page 254 of 920

Dec 22, 2016

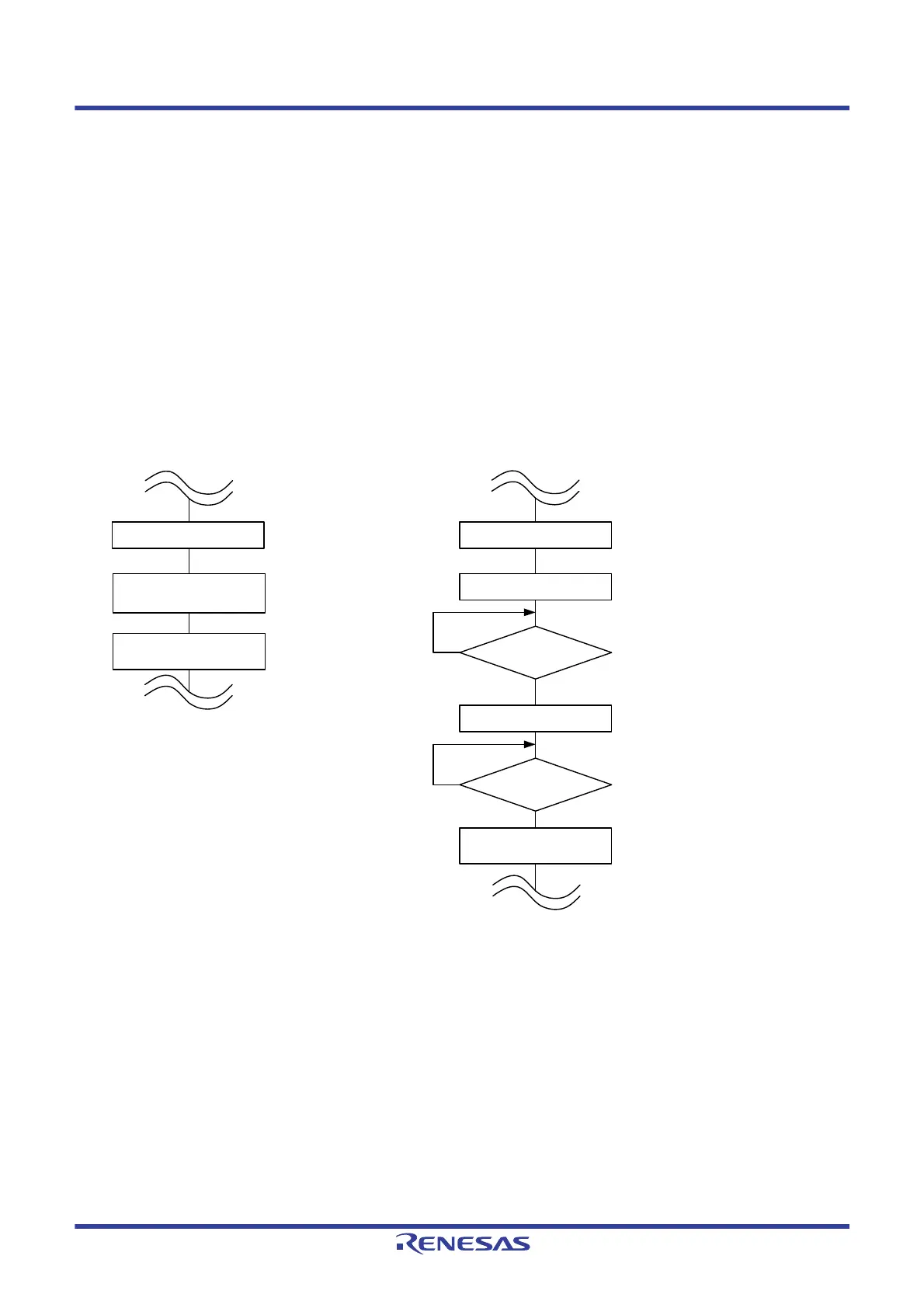

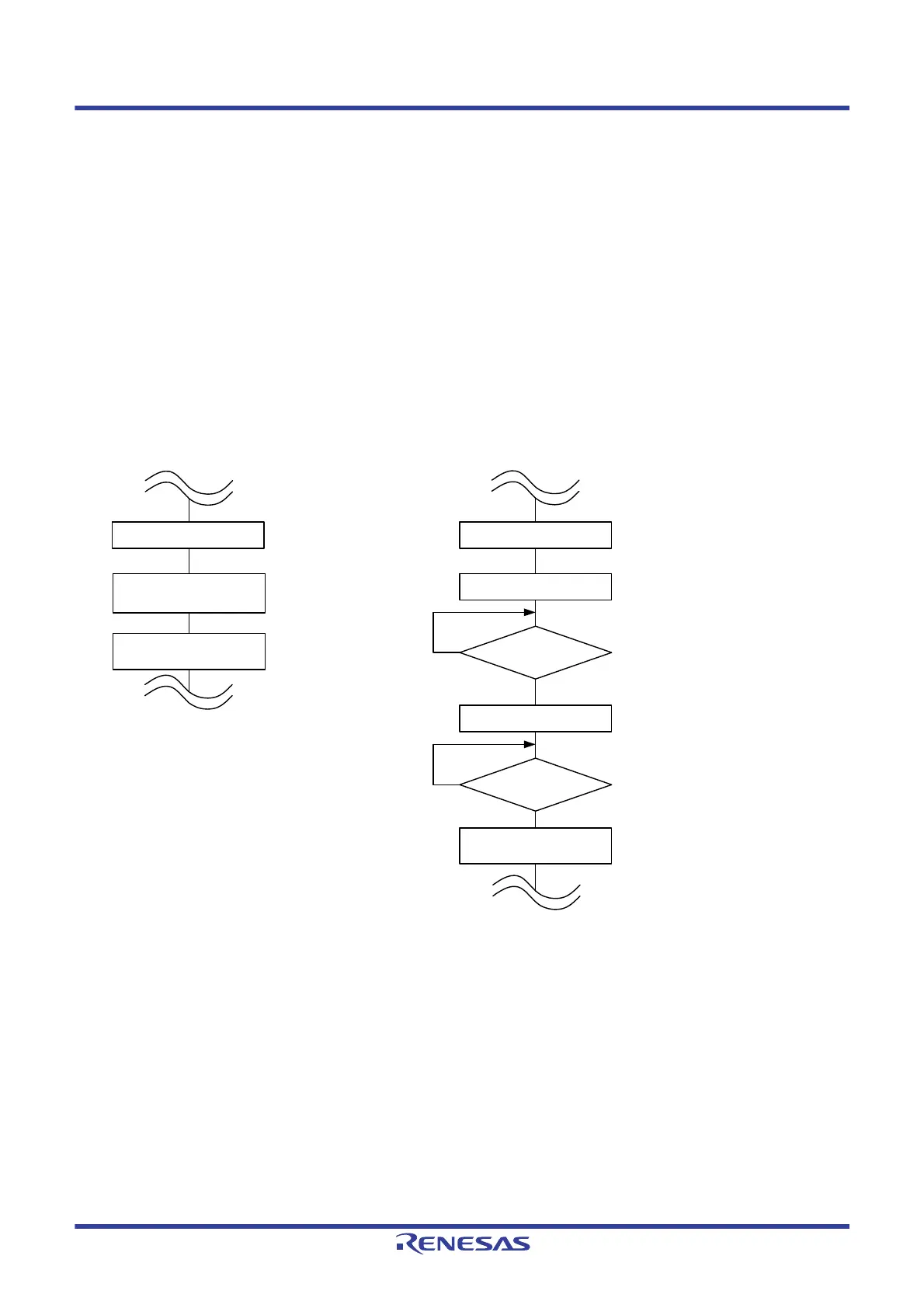

9.4.2 Shifting to HALT/STOP mode after starting operation

Perform one of the following processing when shifting to HALT/STOP mode immediately after setting the RTCE

bit to 1.

However, after setting the RTCE bit to 1, this processing is not required when shifting to HALT/STOP mode after

INTRTC interrupt has occurred.

• Shifting to HALT/STOP mode when at least two count clock (f

RTC) have elapsed after setting the RTCE bit to 1

(see Figure 9 - 19, Example 1).

• Checking by polling the RWST bit to become 1, after setting the RTCE bit to 1 and then setting the RWAIT bit to

1. Afterward, setting the RWAIT bit to 0 and shifting to HALT/STOP mode after checking again by polling that

the RWST bit has become 0 (see Figure 9 - 19, Example 2).

Figure 9 - 19 Procedure for Shifting to HALT/STOP Mode After Setting RTCE bit to 1

Sets to counter

operation start

Waiting at least for 2

f

RTC clocks

Shifts to HALT/STOP

mode

HALT/STOP instruction

execution

Sets to counter operation start

Sets to stop the SEC to YEAR

counters, reads the counter value,

write mode

RWST = 1 ?

RTCE = 1

RWAIT = 1

RWAIT = 0

RWST = 0 ?

HALT/STOP instruction

execution

Checks the counter wait status

Sets the counter operation

Shifts to HALT/STOP mode

No

No

Yes

Example 1

Example 2

Yes

RTCE = 1

Loading...

Loading...