RL78/G1H CHAPTER 10 12-BIT INTERVAL TIMER

R01UH0575EJ0120 Rev. 1.20 Page 265 of 920

Dec 22, 2016

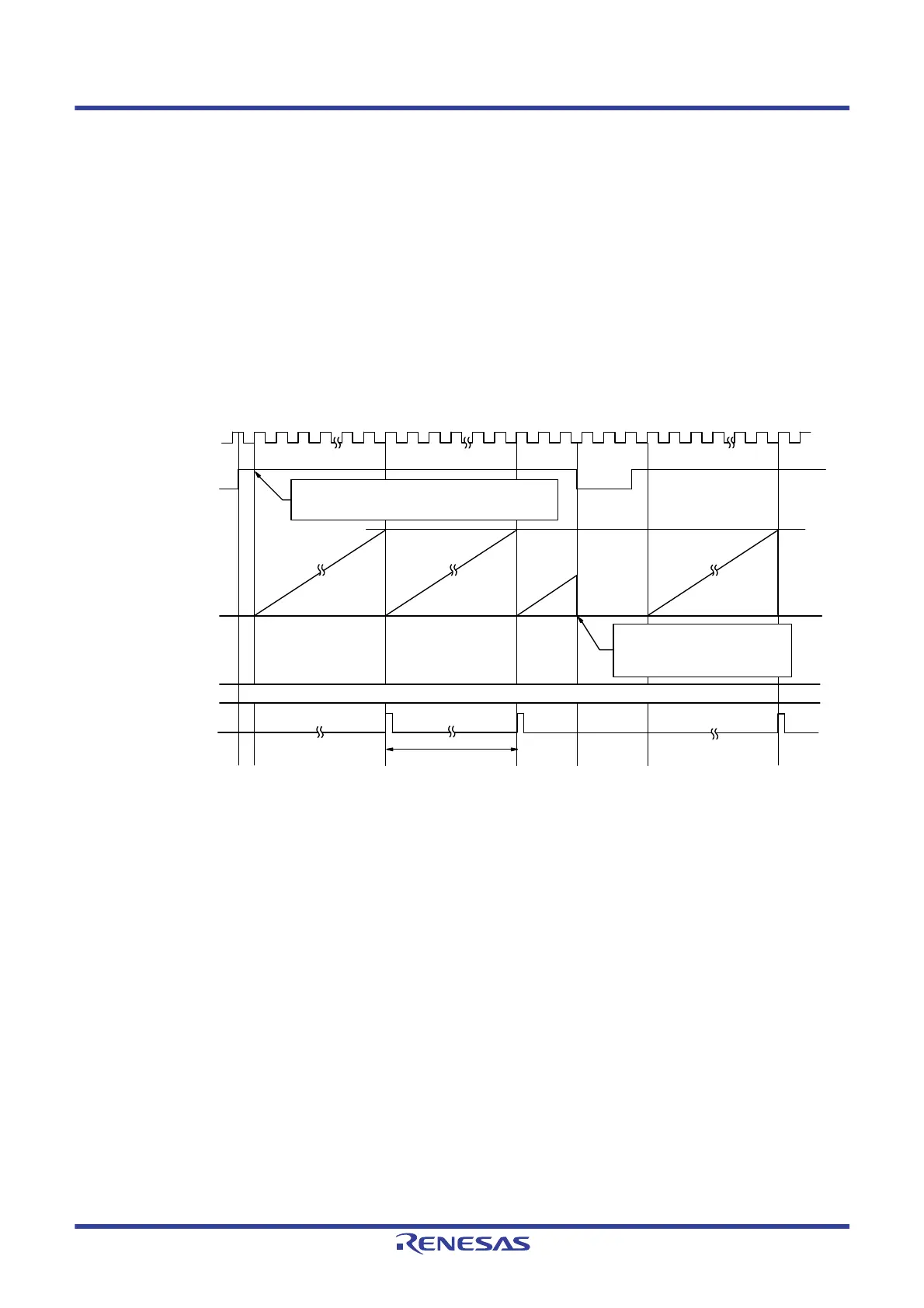

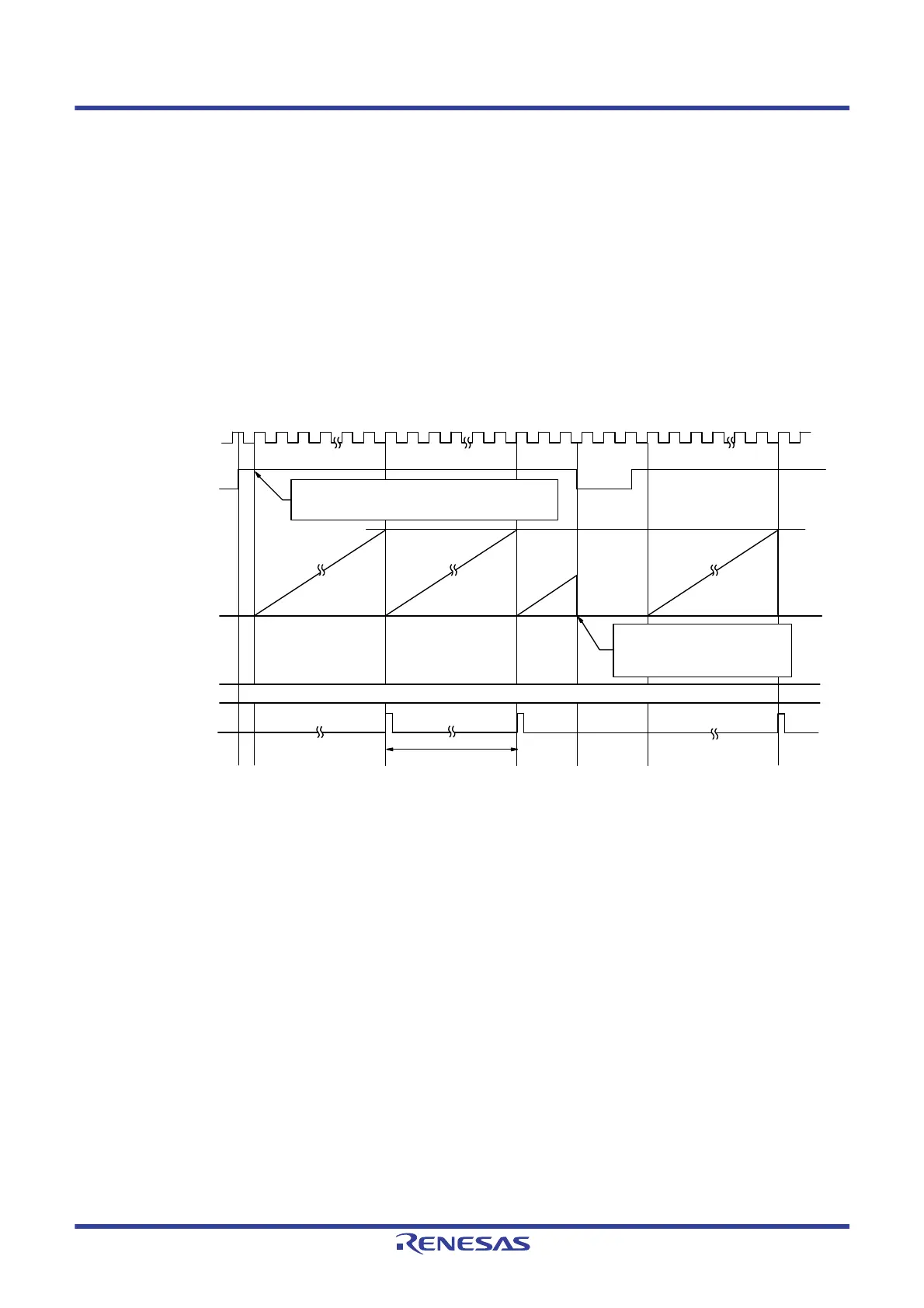

10.4 12-bit Interval Timer Operation

10.4.1 12-bit interval timer operation timing

The count value specified for the ITCMP11 to ITCMP0 bits is used as an interval to operate an 12-bit interval timer

that repeatedly generates interrupt requests (INTIT).

When the RINTE bit is set to 1, the 12-bit counter starts counting.

When the 12-bit counter value matches the value specified for the ITCMP11 to ITCMP0 bits, the 12-bit counter value

is cleared to 0, counting continues, and an interrupt request signal (INTIT) is generated at the same time.

The basic operation of the 12-bit interval timer is as follows.

Figure 10 - 5 12-bit Interval Timer Operation Timing (ITCMP11 to ITCMP0 = 0FFH, count clock: f

SUB = 32.768 kHz)

0FFH

0FFH

Period (7.81 ms)

The 12-bit counter is cleared

asynchronously with the count

clock signal when the RINTE bit is

cleared to 0

Count clock

INTIT

ITCMP11 to ITCMP0

12-bit counter

RINTE

000H

Counting starts at the rising edge of the first cycle of

the count clock signal after the RINTE bit is set to 1.

Loading...

Loading...