RL78/G1H CHAPTER 15 SERIAL INTERFACE IICA

R01UH0575EJ0120 Rev. 1.20 Page 460 of 920

Dec 22, 2016

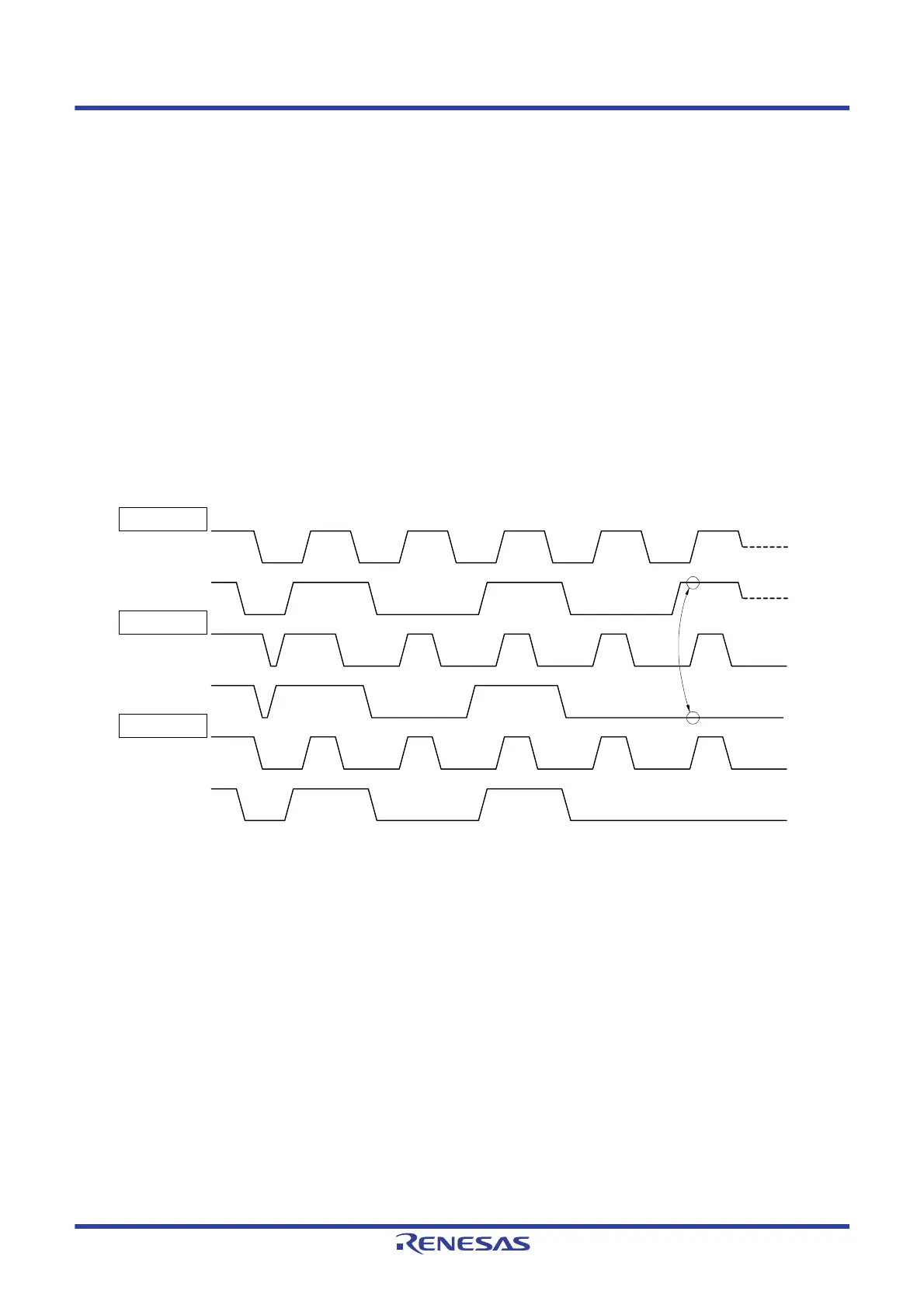

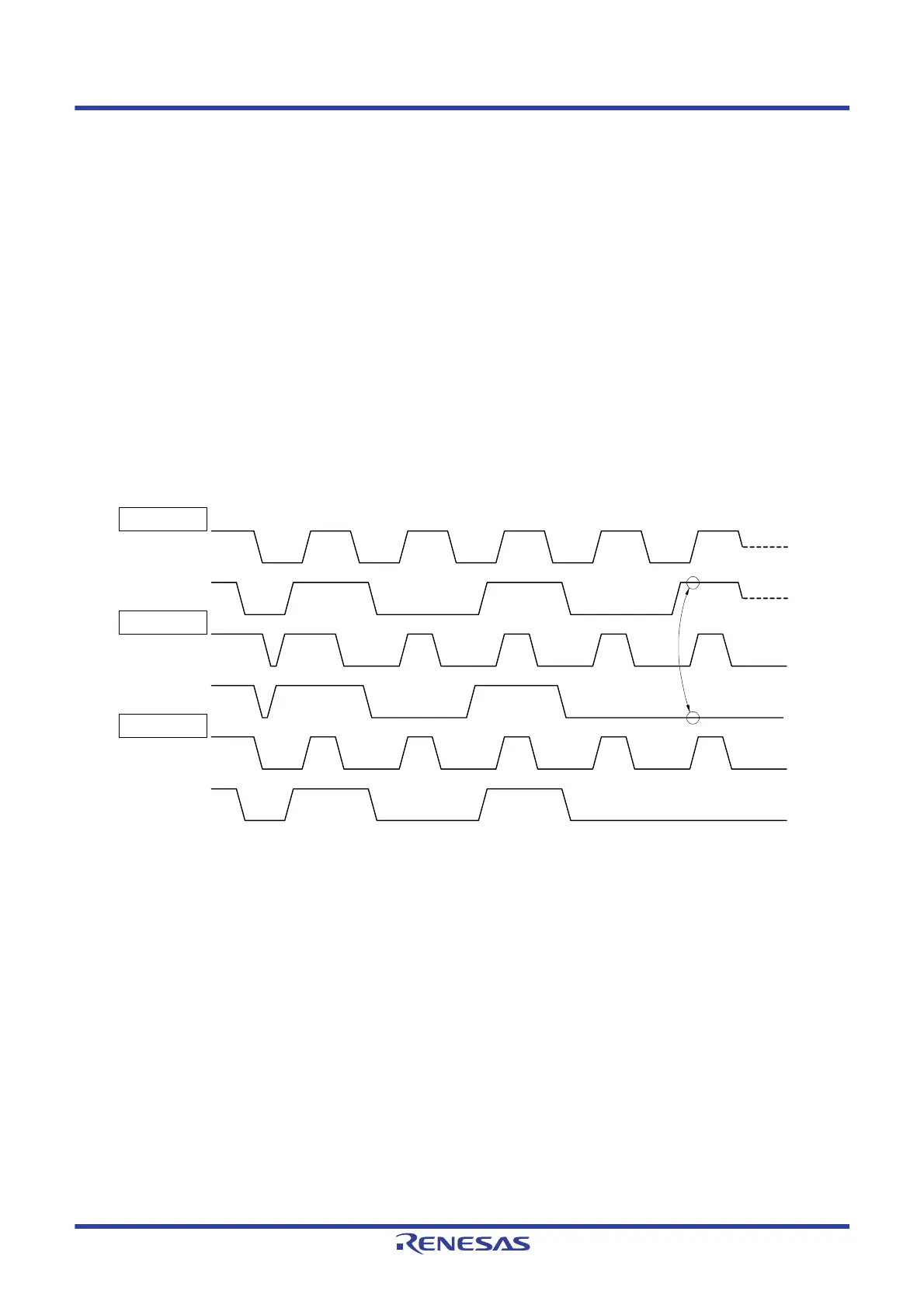

15.5.12 Arbitration

When several master devices simultaneously generate a start condition (when the STTn bit is set to 1 before the

STDn bit is set to 1), communication among the master devices is performed as the number of clocks are

adjusted until the data differs. This kind of operation is called arbitration.

When one of the master devices loses in arbitration, an arbitration loss flag (ALDn) in the IICA status register n

(IICSn) is set (1) via the timing by which the arbitration loss occurred, and the SCLAn and SDAAn lines are both

set to high impedance, which releases the bus.

The arbitration loss is detected based on the timing of the next interrupt request (the eighth or ninth clock, when

a stop condition is detected, etc.) and the ALDn = 1 setting that has been made by software.

For details of interrupt request timing, see 15.5.8 Interrupt request (INTIICAn) generation timing and wait

control.

Remark STDn: Bit 1 of IICA status register n (IICSn)

STTn: Bit 1 of IICA control register n0 (IICCTLn0)

Figure 15 - 27 Arbitration Timing Example

Remark n = 0, 1

SCLAn

SDAAn

SCLAn

SDAAn

SCLAn

SDAAn

Hi-Z

Hi-Z

Master 1 loses arbitration

Master 1

Master 2

Transfer lines

Loading...

Loading...