RL78/G1H CHAPTER 16 DATA TRANSFER CONTROLLER (DTC)

R01UH0575EJ0120 Rev. 1.20 Page 537 of 920

Dec 22, 2016

16.5.5 Number of DTC Execution Clock Cycles

Table 16 - 9 lists the Operations Following DTC Activation and Required Number of Cycles for each operation.

Note 1. For the number of clock cycles required for control data write-back, refer to Table 16 - 10 Number of Clock Cycles

Required for Control Data Write-Back Operation

.

Note 2. For the number of clock cycles required for data read/write, refer to Table 16 - 11 Number of Clock Cycles Required for

One Data Read/Write Operation

.

Remark j = 0 to 23; X: 0 or 1

Note The number of wait states differs depending on the specifications of the register allocated to the extended special

function register (2nd SFR) to be accessed.

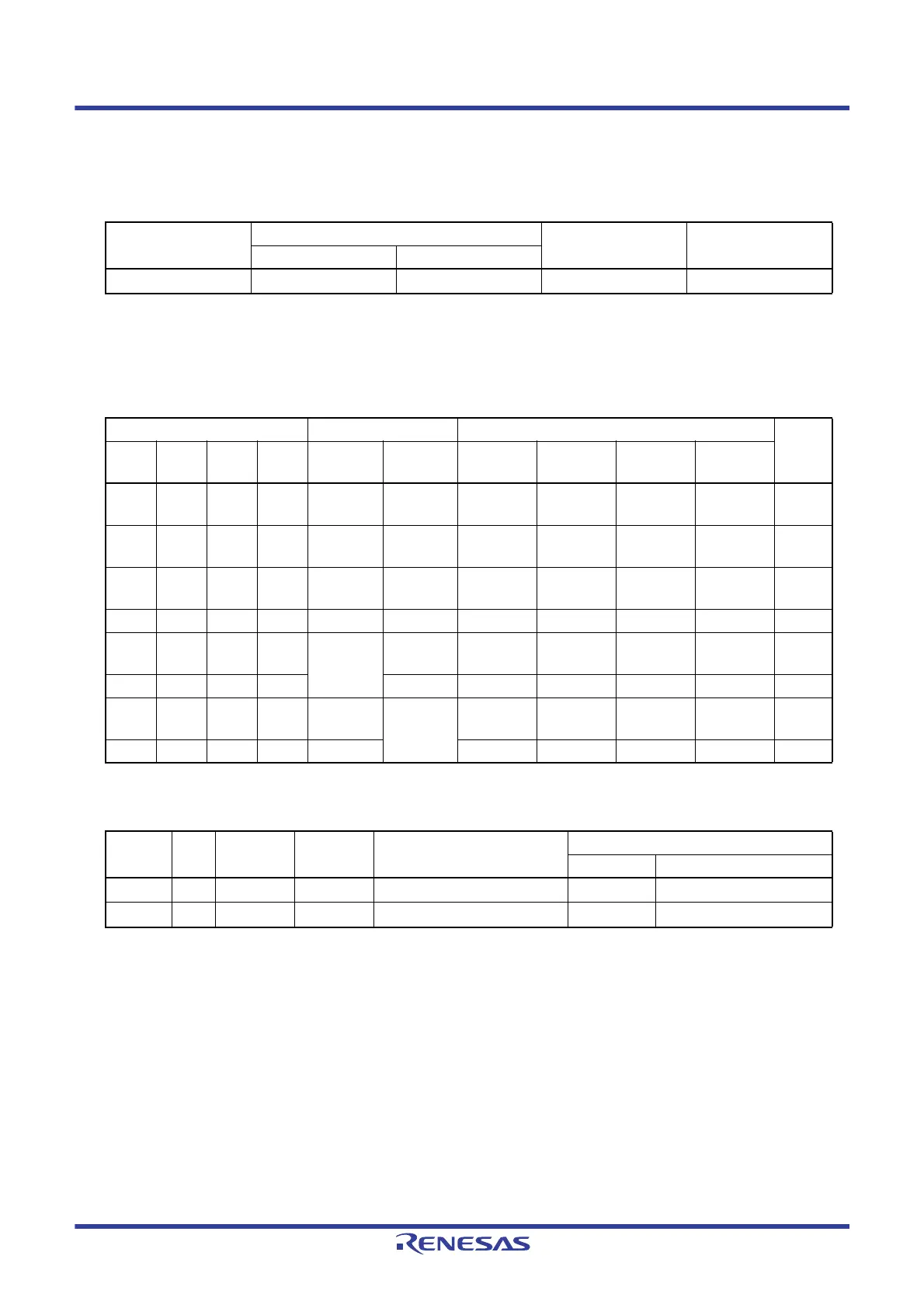

Table 16 - 9 Operations Following DTC Activation and Required Number of Cycles

Vector Read

Control Data

Data Read Data Write

Read Write-back

14

Note 1Note 2Note 2

Table 16 - 10 Number of Clock Cycles Required for Control Data Write-Back Operation

DTCCR Register Setting Address Setting Control Register to be Written Back

Number

of Clock

Cycles

DAMOD SAMOD RPTSEL

MODE Source Destination

DTCCTj

Register

DTRLDj

Register

DTSARj

Register

DTDARj

Register

0 0 X 0 Fixed Fixed Written back Written back

Not written

back

Not written

back

1

01X0

Incremented

Fixed Written back Written back Written back

Not written

back

2

10X0Fixed

Incremented

Written back Written back

Not written

back

Written back 2

11X0

Incremented Incremented

Written back Written back Written back Written back 3

0X11

Repeat

area

Fixed Written back Written back Written back

Not written

back

2

1X11

Incremented

Written back Written back Written back Written back 3

X001Fixed

Repeat

area

Written back Written back

Not written

back

Written back 2

X101

Incremented

Written back Written back Written back Written back 3

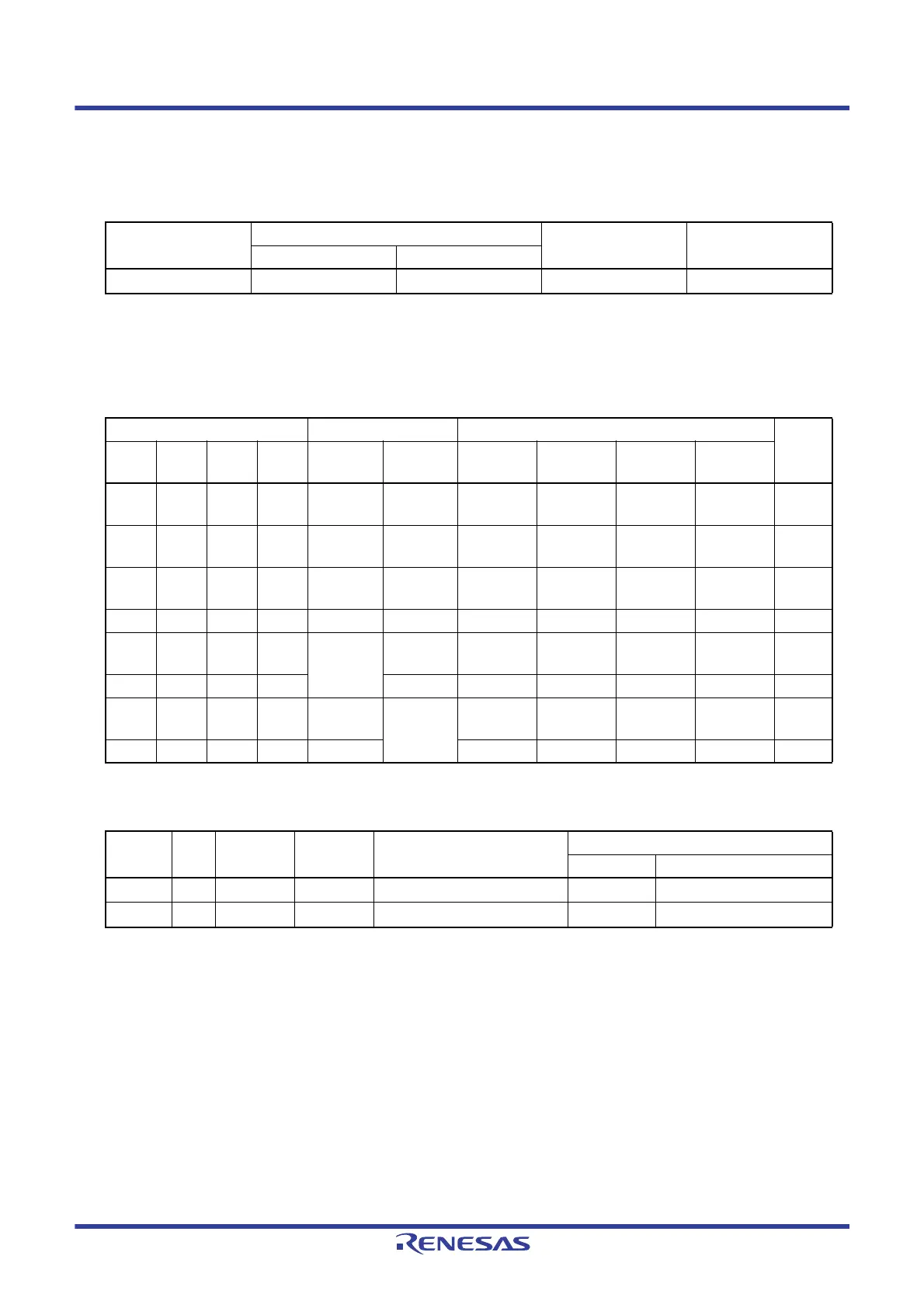

Table 16 - 11 Number of Clock Cycles Required for One Data Read/Write Operation

Operation RAM

Code Flash

Memory

Data Flash

Memory

Special function register (SFR)

Extended special function register (2nd SFR)

No Wait State Wait States

Data read 1 2 4 1 1

1 + number of wait states

Note

Data write 1 — — 1 1

1 + number of wait states

Note

Loading...

Loading...