RL78/G1H CHAPTER 21 RESET FUNCTION

R01UH0575EJ0120 Rev. 1.20 Page 748 of 920

Dec 22, 2016

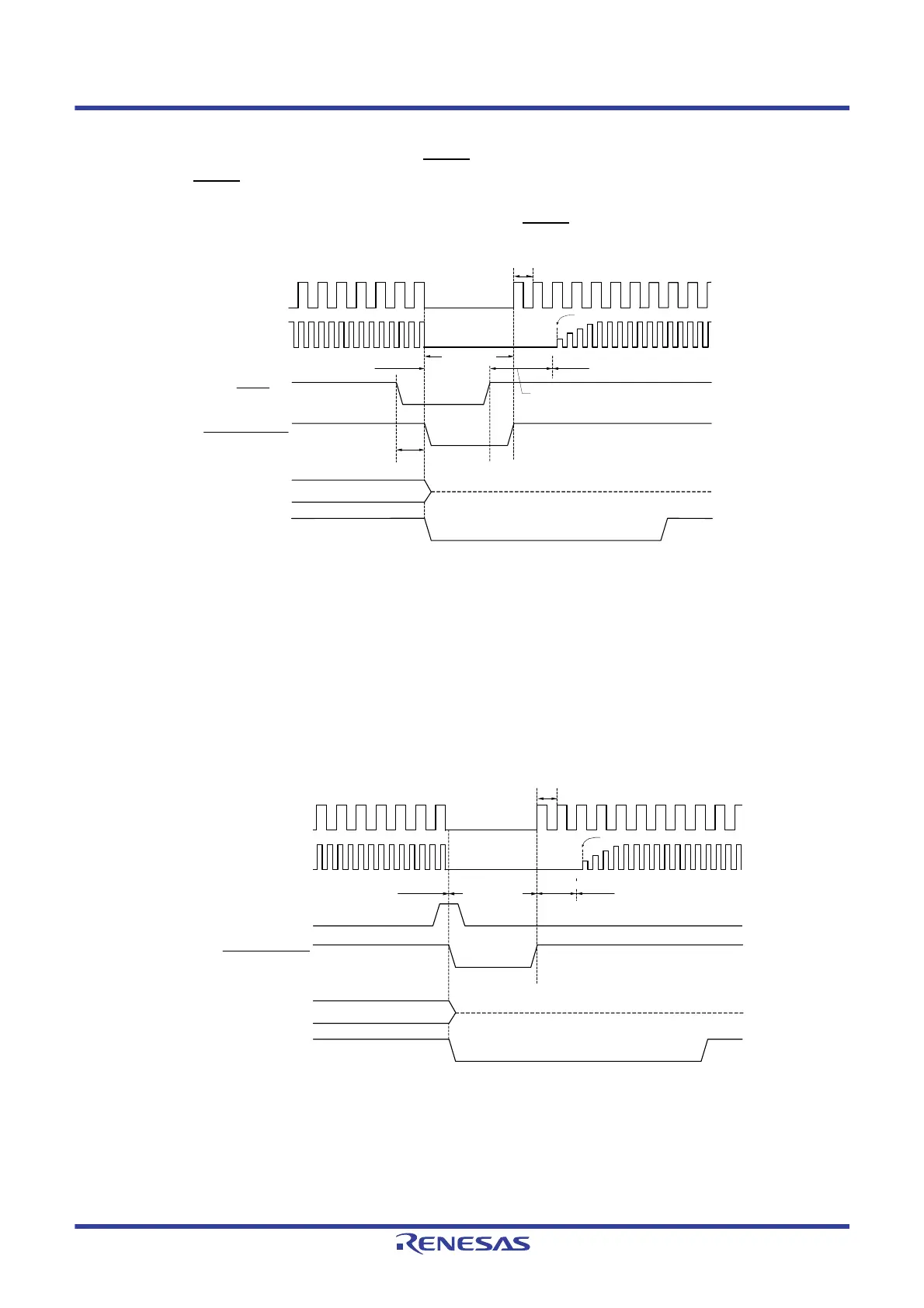

21.1 Timing of Reset Operation

This LSI is reset by input of the low level on the RESET pin and released from the reset state by input of the high

level on the RESET pin. After reset processing, execution of the program with the high-speed on-chip oscillator clock

as the operating clock starts.

Figure 21 - 2 Timing of Reset by RESET

Input

(Notes and Caution are listed on the next page.)

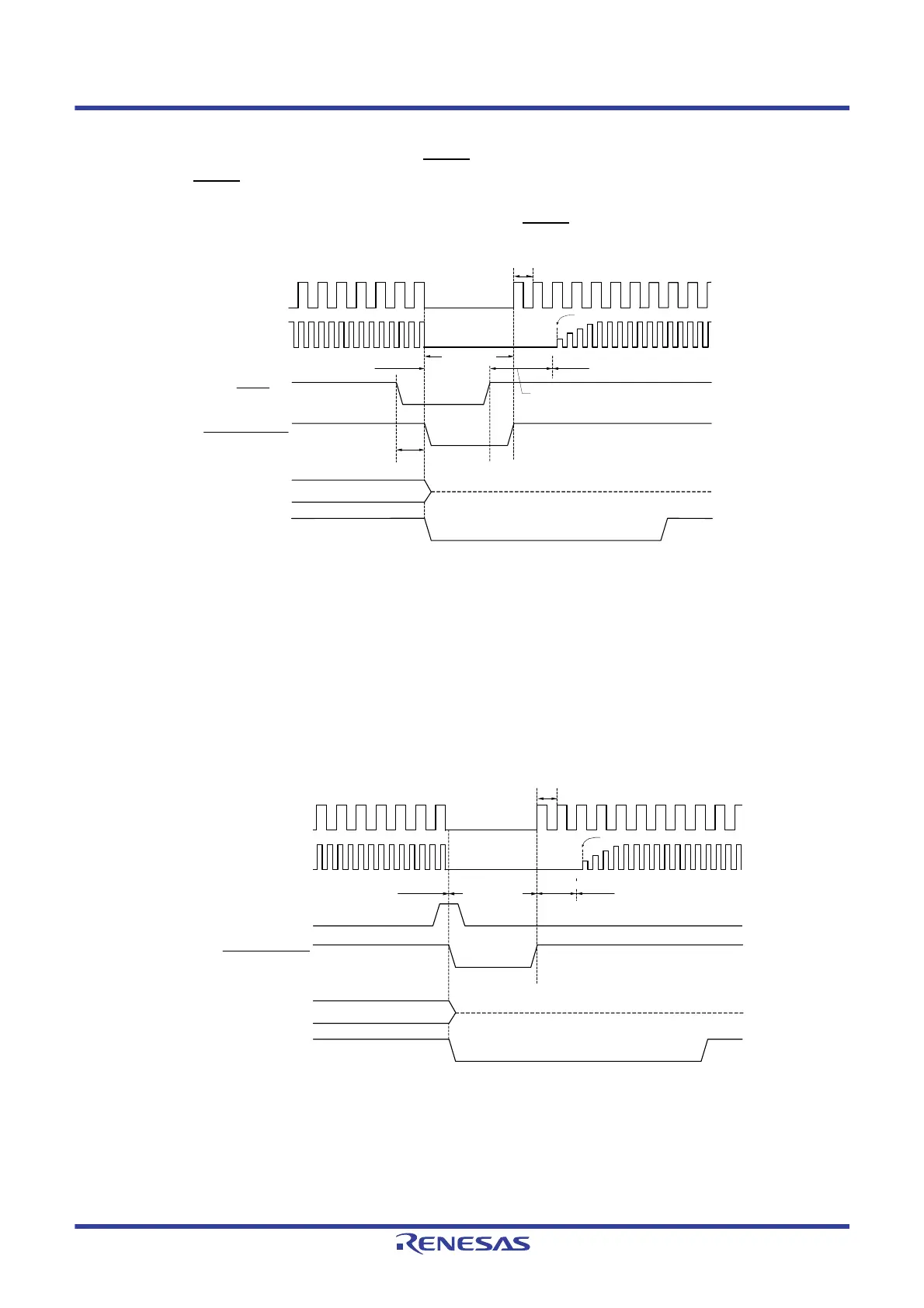

Release from the reset state is automatic in the case of a reset due to a watchdog timer overflow, execution of an

illegal instruction, detection of a RAM parity error, or detection of illegal memory access. After reset processing,

program execution starts with the high-speed on-chip oscillator clock as the operating clock.

Figure 21 - 3 Timing of Reset Due to Watchdog Timer Overflow, Execution of Illegal Instruction,

Detection of RAM Parity Error, or Detection of Illegal Memory Access

(Notes and Caution are listed on the next page.)

Hi-Z

Note 3

Normal operation

CPU status

Reset period

Note 1

High-speed on-chip

oscillator clock

Wait for oscillation accuracy stabilization

Reset processing time when an external reset is released

Note 2

High-speed system clock

(when X1 oscillation is selected)

RESET pin

Internal reset signal

Port pin

(except P130)

Port pin

(P130)

Normal operation

(high-speed on-chip oscillator clock)

Delay

Starting X1 oscillation is specified by software.

CPU status

High-speed on-chip

oscillator clock

High-speed system clock

(when X1 oscillation is selected)

Port pin

(except P130)

Port pin

(P130)

Wait for oscillation accuracy stabilization

Starting X1 oscillation is specified by software.

Internal reset signal

Normal operation

Normal operation

(high-speed on-chip oscillator clock)

Note 1

Hi-Z

Note 3

Watchdog timer overflow/

Execution of illegal instruction/

Detection of RAM parity error/

Detection of illegal memory access

Reset period

(oscillation stop)

0.0511 ms (TYP.)

0.0701 ms (MAX.)

Reset processing

Loading...

Loading...