RL78/G1H CHAPTER 16 DATA TRANSFER CONTROLLER (DTC)

R01UH0575EJ0120 Rev. 1.20 Page 530 of 920

Dec 22, 2016

16.4.1 Activation Sources

The DTC is activated by an interrupt signal from the peripheral functions. The interrupt signals to activate the

DTC are selected with the DTCENi (i = 0 to 4) register.

The DTC sets the corresponding bit among bits DTCENi0 to DTCENi7 in the DTCENi register to 0 (activation

disabled) during operation when the setting of data transfer (the first transfer in chain transfers) is either of the

following:

• A transfer that causes the DTCCTj (j = 0 to 23) register value to change to 0 in normal mode

• A transfer that causes the DTCCTj register value to change to 0 while the RPTINT bit in the DTCCRj register is

1 (interrupt generation enabled) in repeat mode

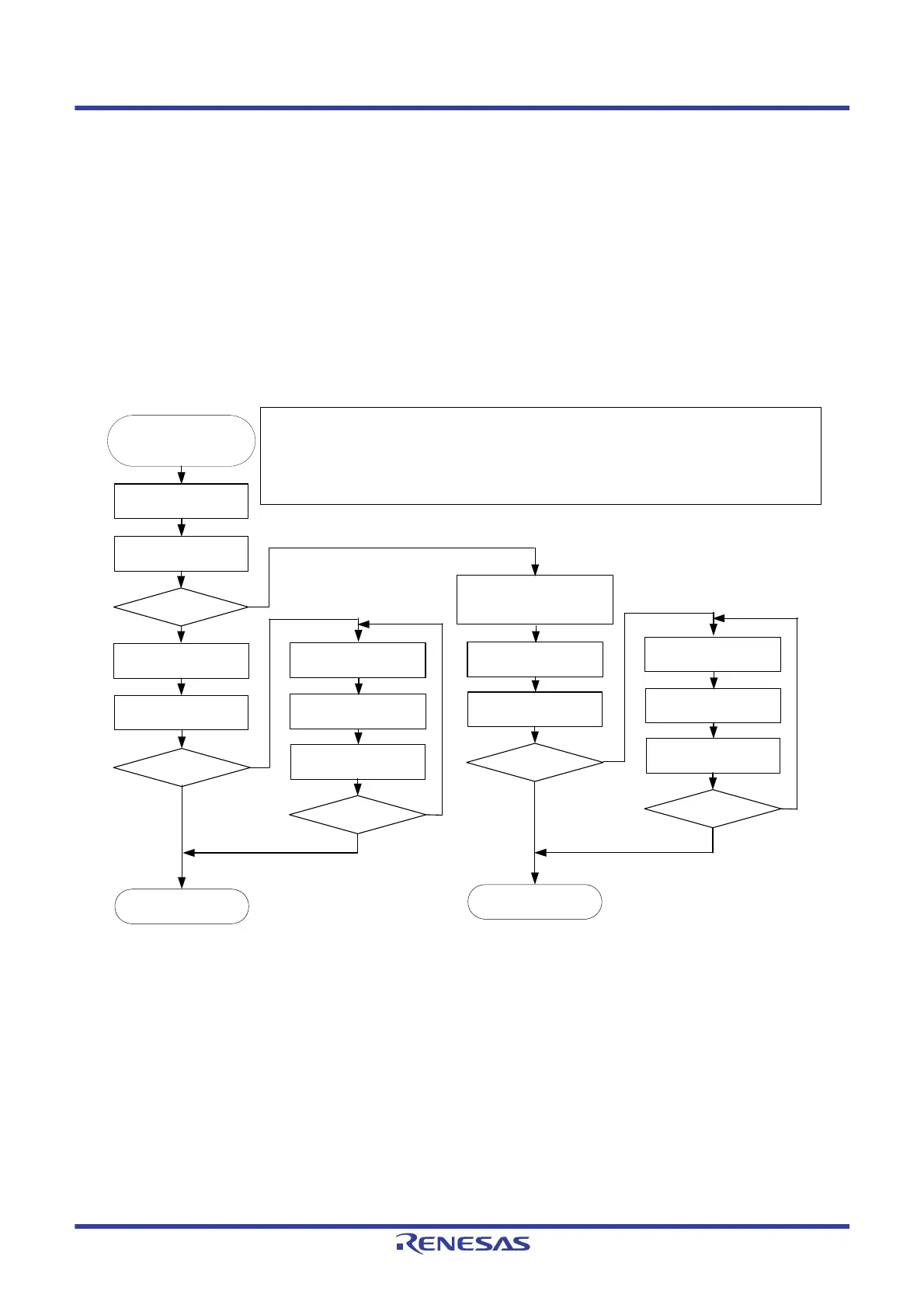

Figure 16 - 14 shows the DTC Internal Operation Flowchart.

Figure 16 - 14 DTC Internal Operation Flowchart

Note 0 is not written to the bit among bits DTCENi0 to DTCENi7 for data transfers activated by the setting to enable chain

transfers (the CHNE bit is 1). Also, no interrupt request is generated.

Transfer data

Branch (1)

Yes

Read control data

Read vector

DTC activation source

generation

Write back

control data

CHNE = 1?

No

Yes

No

Read control data

Transfer data

Write back

control data

CHNE = 1?

Write 0 to the bit among bits

DTCENi0 to DTCENi7

Generate an interrupt request

Transfer data

Write back

control data

CHNE = 1?

Yes

No

Yes

Read control data

Transfer data

Write back

control data

CHNE = 1?

Yes

No

No

Note

End

Interrupt handling

Branch (1)

0 is written to the bit among bits DTCENi0 to DTCENi7 and an interrupt request is generated when

transfer is either of the following:

- A transfer that causes the DTCCTj (j = 0 to 23) register value to change from 1 to 0 in normal mode

- A transfer that causes the DTCCTj register value to change from 1 to 0 while the RPTINT bit is 1 in

repeat mode

Remark DTCENi0 to DTCENi7: Bits in DTCENi (i = 0 to 4) register

RPTINT, CHNE: Bits in DTCCRj (j = 0 to 23) register

Loading...

Loading...