RL78/G15 CHAPTER 6 TIMER ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 213 of 765

Mar 7, 2023

6.6 Channel Output (TOmn pin) Control

6.6.1 TOmn pin output circuit configuration

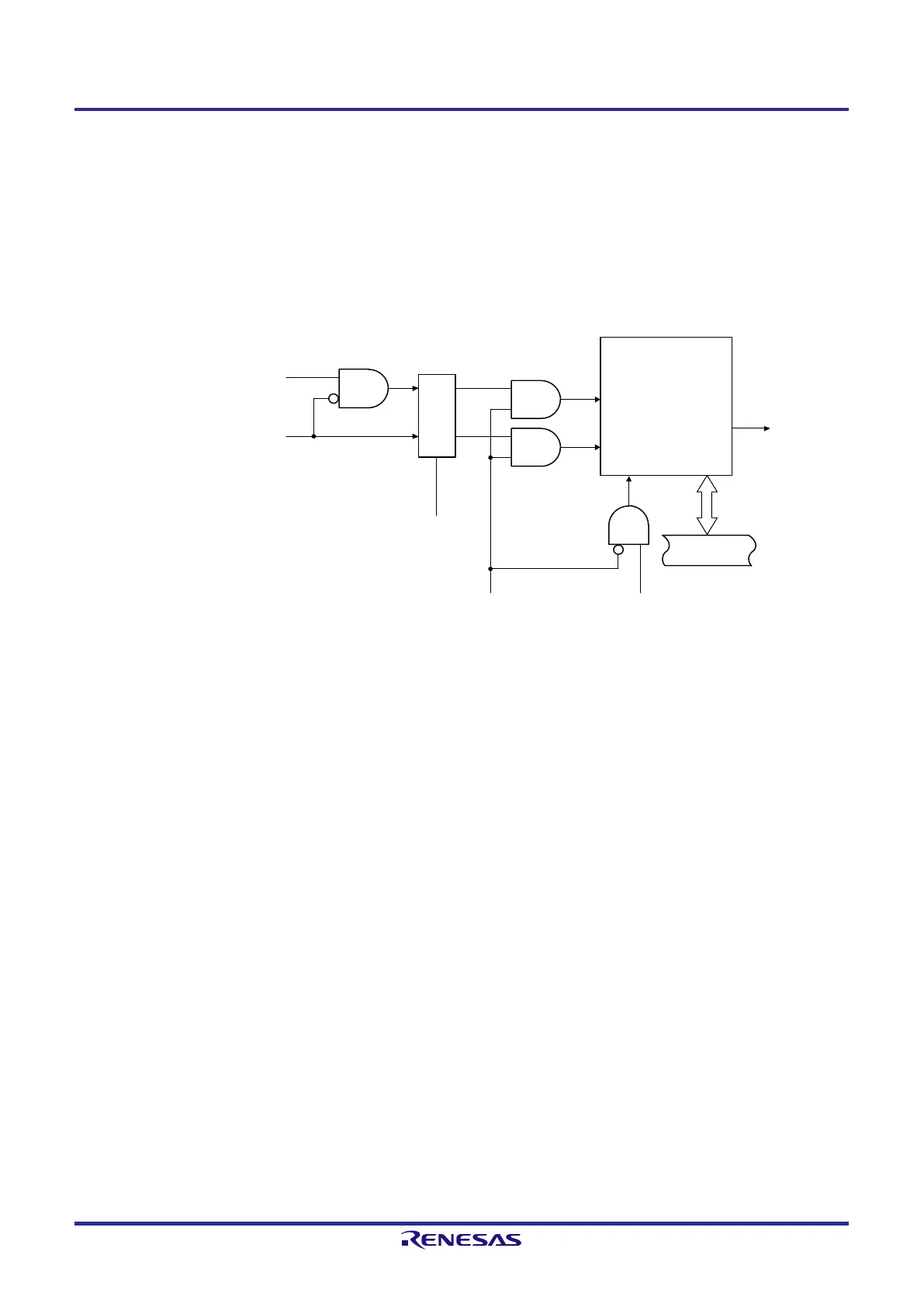

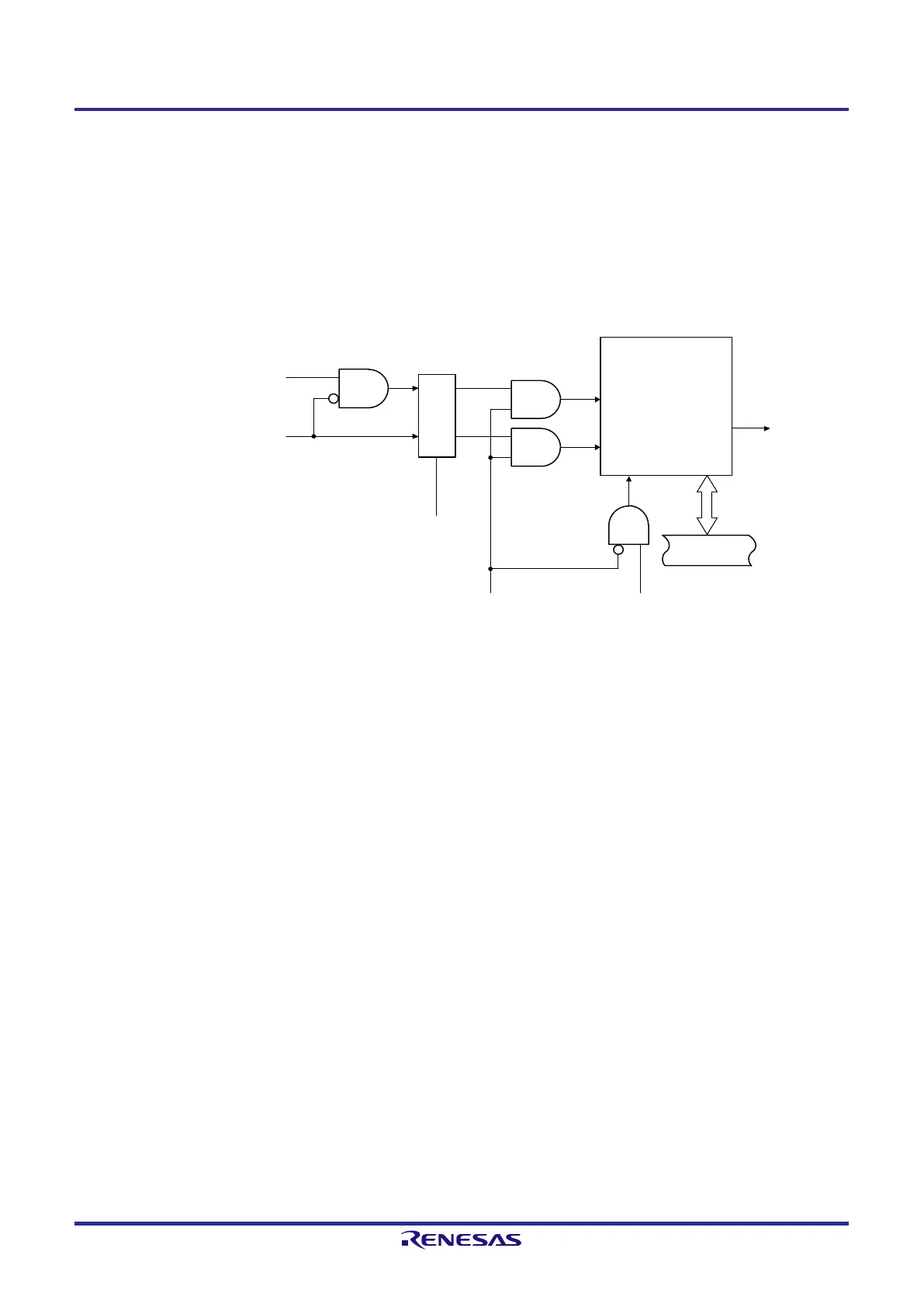

Figure 6-29. Output Circuit Configuration

Internal bus

Interrupt signal of the master channel

(

INTTMmn

)

TOLmn

TOMmn

TOEmn

<1

>

<2>

<

3

>

<4>

<

5>

TOmn write signal

TOmn pin

TOmn register

Set

Reset/toggle

Interrupt signal of the slave channel

(INTTMmp)

Controller

The following describes the TOmn pin output circuit.

<1> When TOMmn = 0 (master channel output mode), the set value of timer output level register m (TOLm) is

ignored and only INTTMmp (slave channel timer interrupt) is transmitted to timer output register m (TOm).

<2> When TOMmn = 1 (slave channel output mode), both INTTMmn (master channel timer interrupt) and INTTMmp

(slave channel timer interrupt) are transmitted to the TOm register.

At this time, the TOLm register becomes valid and the signals are controlled as follows:

When TOLmn = 0: Positive logic output (INTTMmn → set, INTTMmp → reset)

When TOLmn = 1: Negative logic output (INTTMmn → reset, INTTMmp → set)

When INTTMmn and INTTMmp are simultaneously generated, (0% output of PWM), INTTMmp (reset signal)

takes priority, and INTTMmn (set signal) is masked.

<3> While timer output is enabled (TOEmn = 1), INTTMmn (master channel timer interrupt) and INTTMmp (slave

channel timer interrupt) are transmitted to the TOm register. Writing to the TOm register (TOmn write signal)

becomes invalid.

When TOEmn = 1, the TOmn pin output never changes with signals other than interrupt signals.

To initialize the TOmn pin output level, it is necessary to set timer operation is stopped (TOEmn = 0) and to write

a value to the TOm register.

<4> While timer output is disabled (TOEmn = 0), writing to the TOmn bit to the target channel (TOmn write signal)

becomes valid. When timer output is disabled (TOEmn = 0), neither INTTMmn (master channel timer interrupt)

nor INTTMmp (slave channel timer interrupt) is transmitted to the TOm register.

<5> The TOm register can always be read, and the TOmn pin output level can be checked.

(Remark is listed on the next page.)

Loading...

Loading...