RL78/G15 CHAPTER 6 TIMER ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 215 of 765

Mar 7, 2023

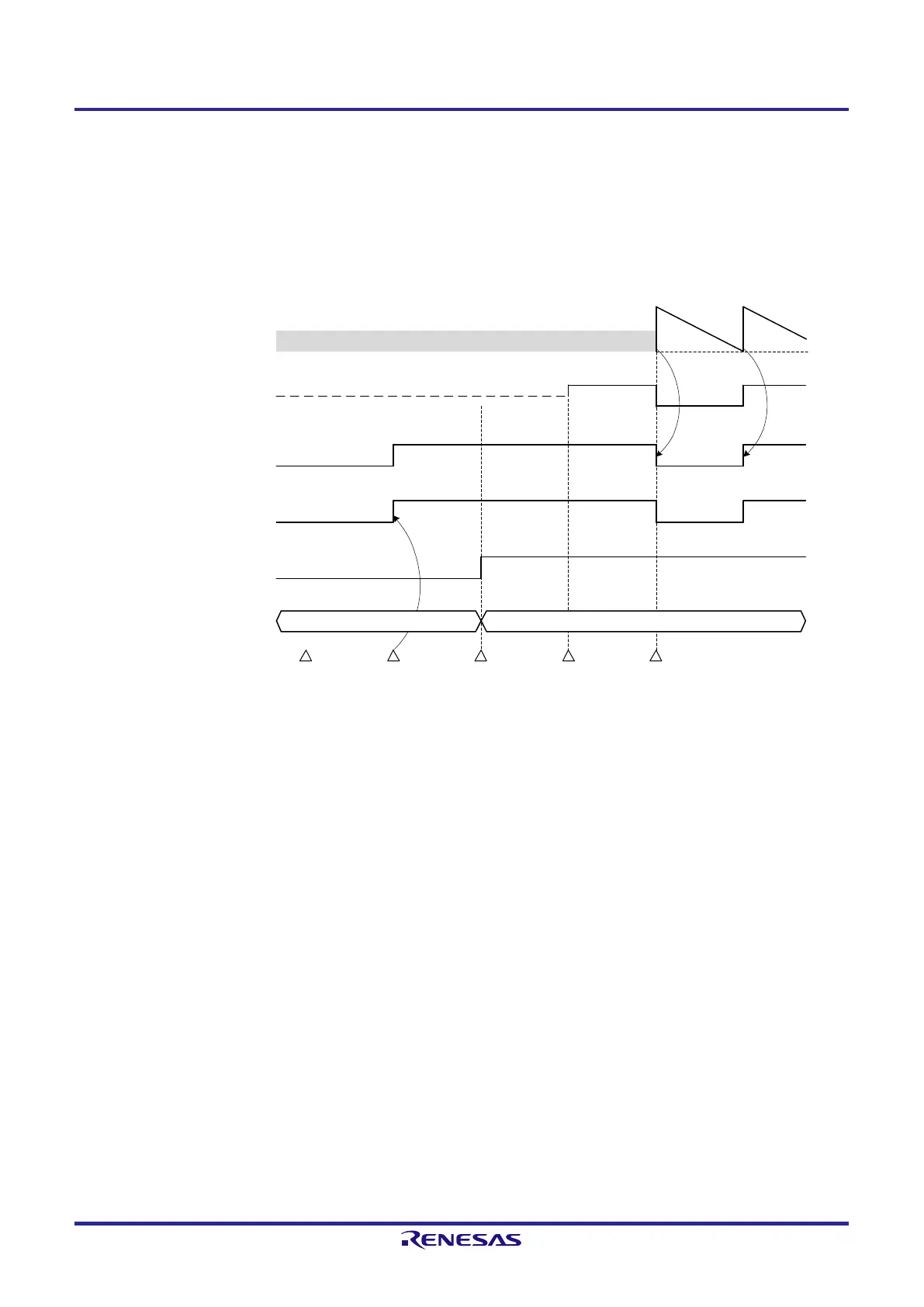

6.6.2 TOmn pin output setting

The following figure shows the procedure and status transition of the TOmn output pin from initial setting to timer

operation start.

Figure 6-30. Status Transition from Timer Output Setting to Operation Start

TCRmn

(Counter)

Timer alternate-function pin

Timer output signal

TOEmn

TOmn

Undefined value (FFFFH after reset)

Write operation disabled period to TOmn

<1>

Set TOMmn

Set TOLmn

<4>, <5>

Set the port to

output mode

<2>

Set TOmn

<3>

Set TOEmn

<6>

Timer operation

start

Hi-Z

Write operation enabled period to TOmn

<1> The operation mode of timer output is set.

●

TOMmn bit (0: Master channel output mode, 1: Slave channel output mode)

●

TOLmn bit (0: Positive logic output, 1: Negative logic output)

<2> The timer output signal is set to the initial status by setting timer output register m (TOm).

<3> The timer output operation is enabled by writing 1 to the TOEmn bit (writing to the TOm register is disabled).

<4> The port is set to digital I/O by port mode control register (PMCxx) (see 6.3.14 Registers controlling port

functions of pins to be used for timer I/O).

<5> The port I/O setting is set to output (see 6.3.14 Registers controlling port functions of pins to be used for

timer I/O).

<6> The timer operation is enabled (TSmn = 1).

Remark m: Unit number (m = 0), n: Channel number (n = 0 to 7)

Loading...

Loading...