RL78/G15 CHAPTER 6 TIMER ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 225 of 765

Mar 7, 2023

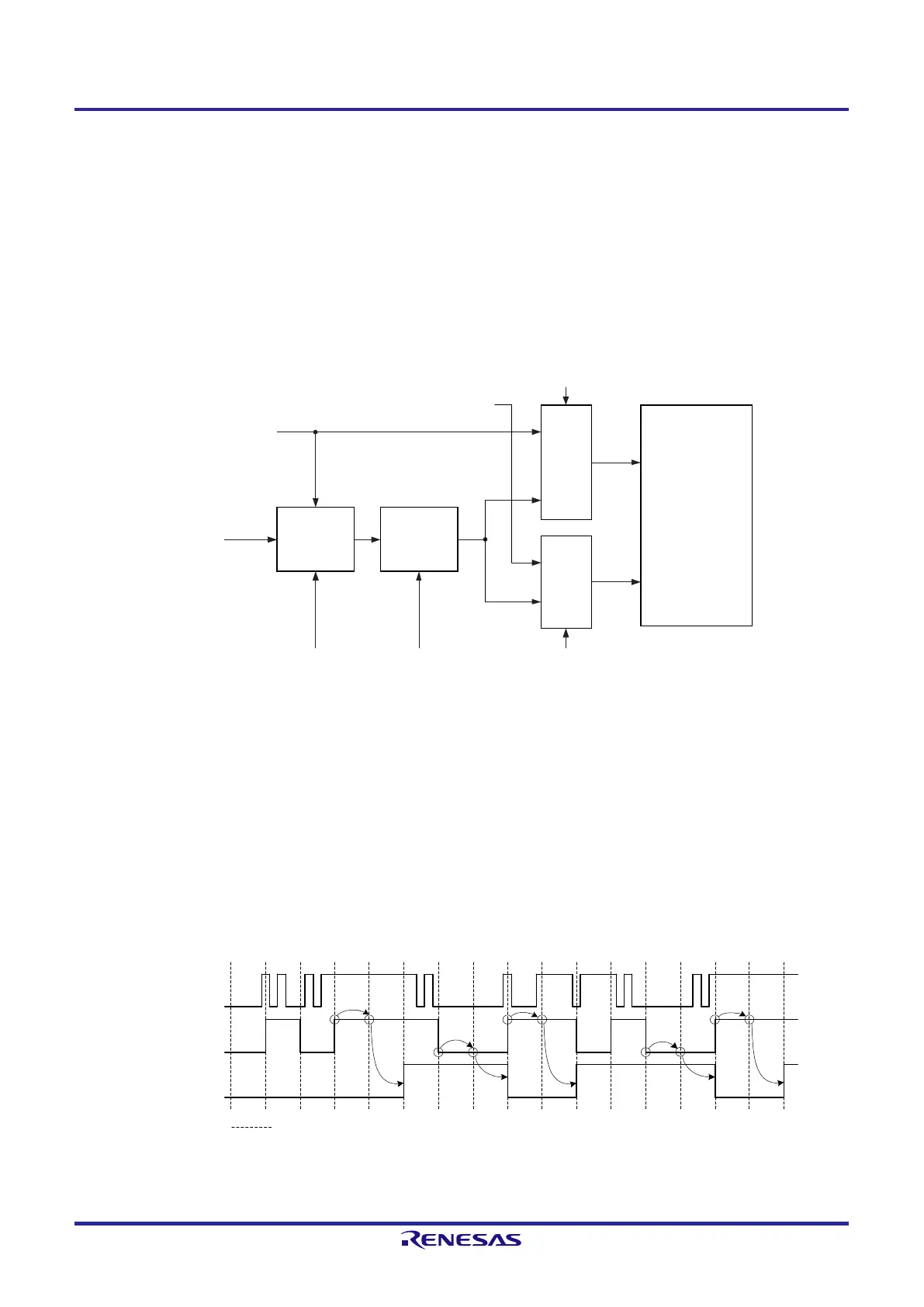

6.7 Timer Input (TImn) Control

6.7.1 TImn input circuit configuration

A signal is input from a timer input pin, goes through a noise filter and an edge detector, and is sent to a timer controller.

Enable the noise filter for the pin in need of noise removal. The following shows the configuration of the input circuit.

Figure 6-38. Input Circuit Configuration

Noise filter

Timer controller

CCSmn

f

TCLK

f

MCK

TImn pin

TNFENmn CISmn1,

CISmn0

STSmn2 to

STSmn0

Edge

detection

Interrupt signal from master channel

Count clock

selection

Trigger

selection

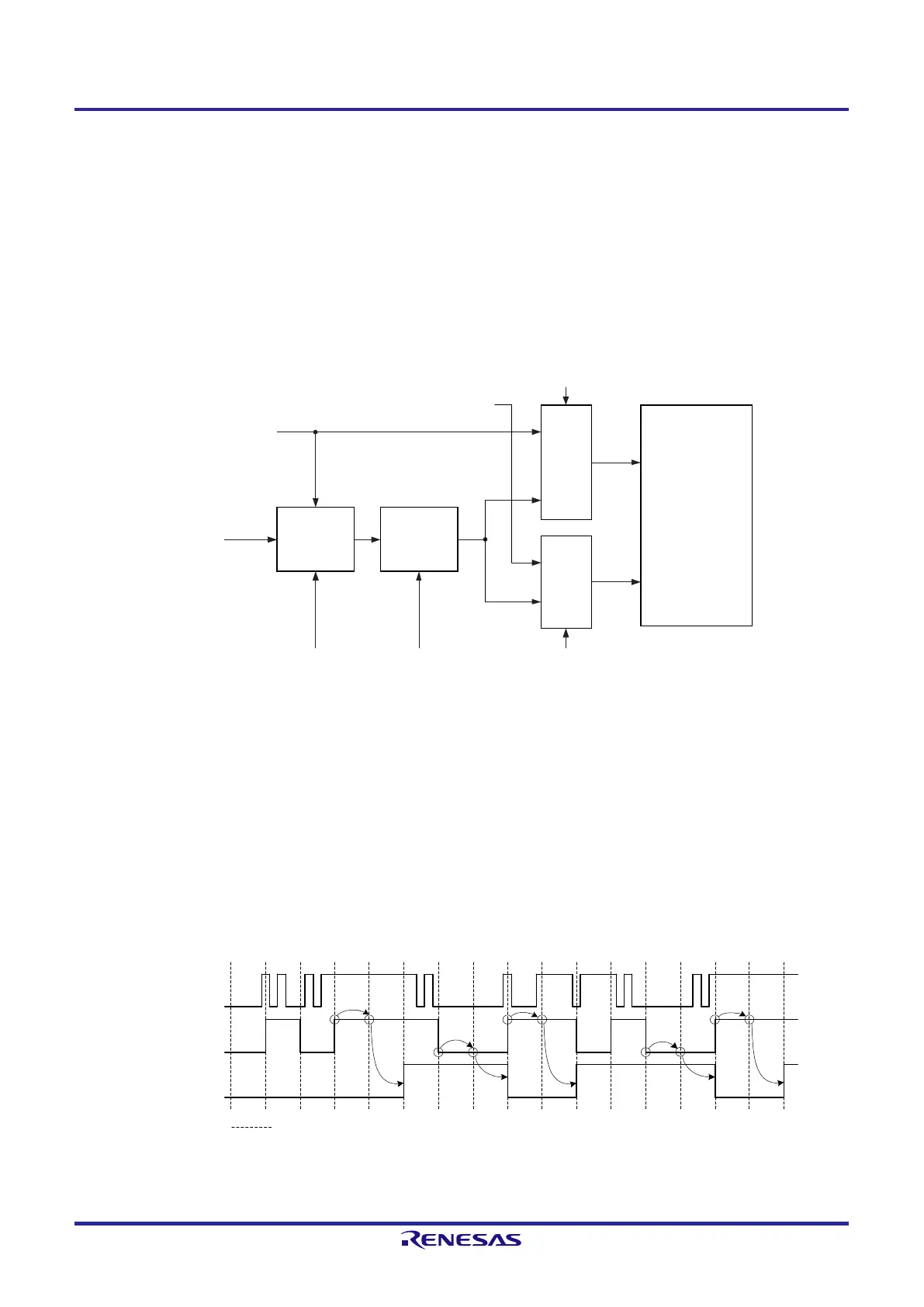

6.7.2 Noise filter

When the noise filter is disabled, the input signal is only synchronized with the operation clock (f

MCK

) for channel n. When

the noise filter is enabled, after synchronization with the operation clock (f

MCK

) for channel n, whether the signal keeps

the same value for two clock cycles is detected. The following shows differences in waveforms output from the noise filter

between when the noise filter is enabled and disabled.

Figure 6-39. Sampling Waveforms through TImn Input Pin with Noise Filter Enabled and Disabled

TImn pin

Noise filter disabled

Noise filter enabled

Operation clock (f

MCK

)

Loading...

Loading...