RL78/G15 CHAPTER 7 12-BIT INTERVAL TIMER

R01UH0959EJ0110 Rev.1.10 Page 302 of 765

Mar 7, 2023

7.3.2 Operation speed mode control register (OSMC)

The WUTMMCK0 bit can be used to control supply of the 12-bit interval timer count clock.

Set the WUTMMCK0 bit to 1 before operating the 12-bit interval timer. Do not clear the WUTMMCK0 bit to 0 before

counter operation has stopped.

The OSMC register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

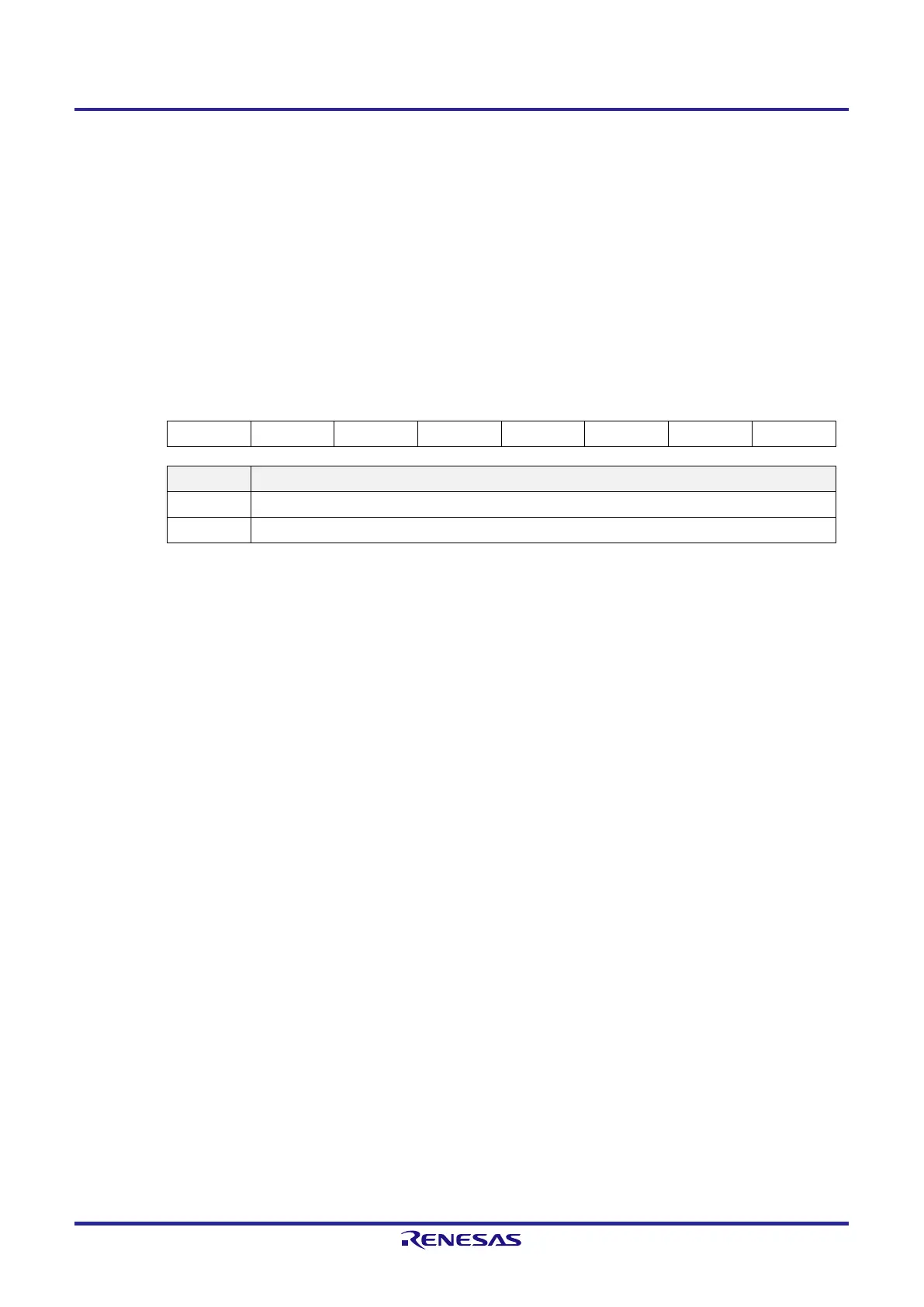

Figure 7-3. Format of Operation Speed Mode Control Register (OSMC)

Address: F00F3H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

OSMC 0 0 0 WUTMMCK0 0 0 0 0

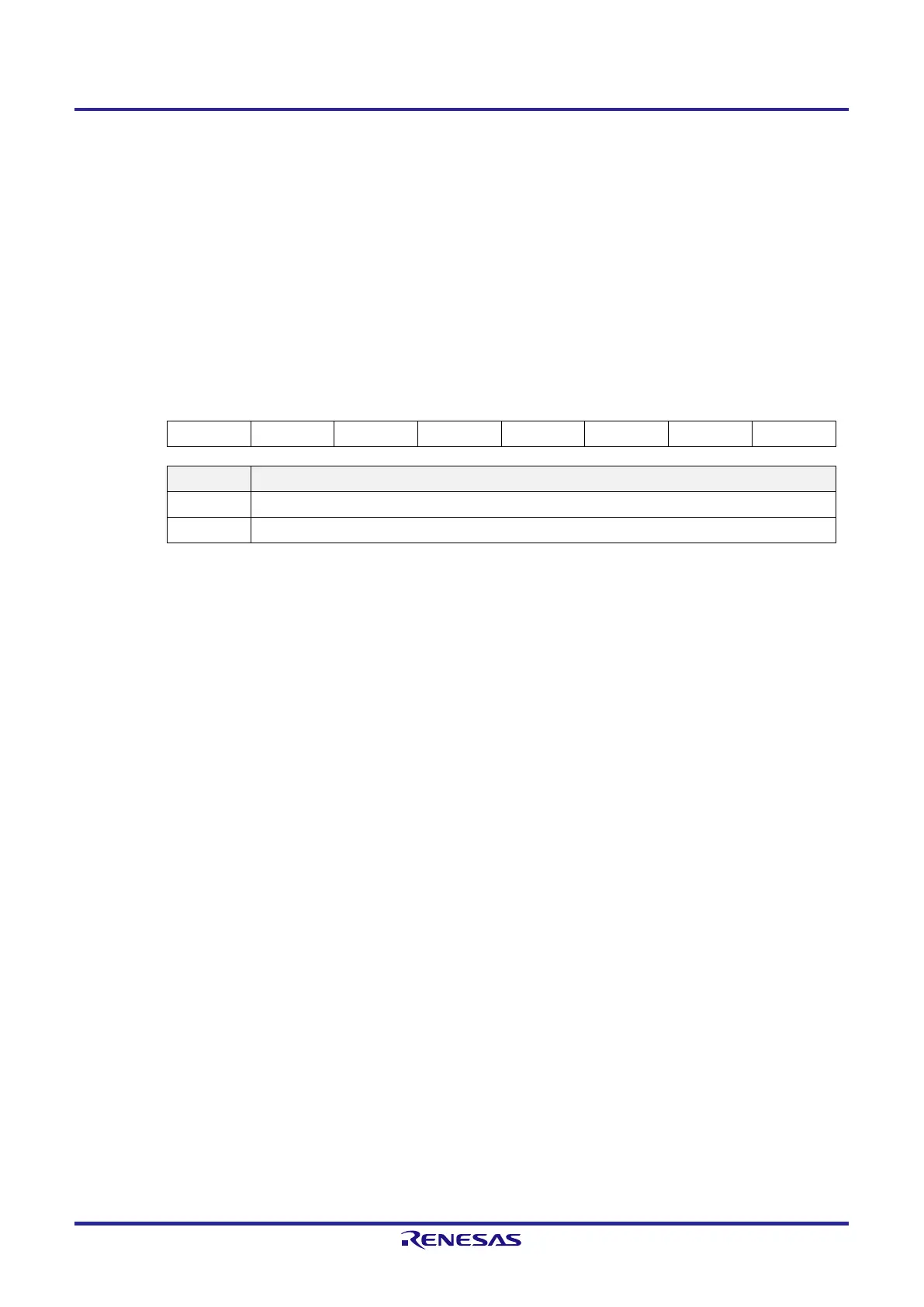

WUTMMCK0 Supply of the count clock for 12-bit interval timer

0 Clock supply stop.

1 Low-speed on-chip oscillator clock (f

IL

) supply

Loading...

Loading...